InitEPwm (void)

{

EALLOW;

SysCtrlRegs. PCLKCR0. Bit. TBCLKSYNC=0;

EDIS.

//EPWM Module 1 config - PWMA1 + PWMB1

EPwm1Regs. TBPRD=PWM_PRD;//Set the timer period

EPwm1Regs. TBPHS. Half. TBPHS=0 x0000;//Phase is 0

EPwm1Regs. TBCTR=0 x0000;//the Clear counter

//Setup TBCLK

EPwm1Regs. TBCTL. Bit. CTRMODE=TB_COUNT_UPDOWN;//Count updown

EPwm1Regs. TBCTL. Bit. PHSEN=TB_DISABLE;//Disable phase loading

EPwm1Regs. TBCTL. Bit. PRDLD=0;

EPwm1Regs. TBCTL. Bit. SYNCOSEL=TB_CTR_ZERO;

EPwm1Regs. TBCTL. Bit. HSPCLKDIV=TB_DIV1;//Clock thewire to SYSCLKOUT

EPwm1Regs. TBCTL. Bit. CLKDIV=TB_DIV1;

EPwm1Regs. TBCTL. Bit. PRDLD=0;//when the CTR=0, time base TBPRD register cycle loading shadow register values (new)

EPwm1Regs. CMPCTL. Bit. SHDWAMODE=CC_SHADOW;//Counter - compare shadow mode

EPwm1Regs. CMPCTL. Bit. SHDWBMODE=CC_SHADOW;

EPwm1Regs. CMPCTL. Bit. LOADAMODE=CC_CTR_ZERO;//the Load registers every ZERO

EPwm1Regs. CMPCTL. Bit. LOADBMODE=CC_CTR_ZERO;

//Setup compare

EPwm1Regs. CMPA. Half. CMPA=PWM_PRD/4;

EPwm1Regs. CMPB=0 XFFFF;

//Set the actions

EPwm1Regs. AQCTLA. Bit. CAU=0 x3;//Set PWM1A on Zero AQ_CLEAR

EPwm1Regs. AQCTLA. Bit. CAD=0 x3;//AQ_SET

EPwm1Regs. AQCTLB. Bit. CAU=AQ_CLEAR;//Set PWM1B on Zero

EPwm1Regs. AQCTLB. Bit. CAD=AQ_SET;

////Active Low PWMs - Setup Deadband

EPwm1Regs. DBCTL. Bit. OUT_MODE=DB_FULL_ENABLE;

EPwm1Regs. DBCTL. Bit. POLSEL=DB_ACTV_HIC;

EPwm1Regs. DBCTL. Bit. IN_MODE=0 x2.

//EPwm1Regs. DBRED=DEADTIME;

//EPwm1Regs. DBFED=DEADTIME;

//EPWM Module 2 config - PWMA2 + PWMB2

EPwm2Regs. TBPRD=PWM_PRD;//Set the timer period

EPwm2Regs. TBPHS. Half. TBPHS=0 x0000;//Phase is 0

EPwm2Regs. TBCTR=0 x0000;//the Clear counter

//Setup TBCLK

EPwm2Regs. TBCTL. Bit. CTRMODE=TB_COUNT_UPDOWN;//Count updown

EPwm2Regs. TBCTL. Bit. PHSEN=TB_DISABLE;//Disable phase loading

EPwm2Regs. TBCTL. Bit. SYNCOSEL=TB_CTR_ZERO;

EPwm2Regs. TBCTL. Bit. HSPCLKDIV=TB_DIV1;//Clock thewire to SYSCLKOUT

EPwm2Regs. TBCTL. Bit. CLKDIV=TB_DIV1;

EPwm2Regs. TBCTL. Bit. PRDLD=0;//when the CTR=0, time base TBPRD register cycle loading shadow register values (new)

EPwm2Regs. CMPCTL. Bit. SHDWAMODE=CC_SHADOW;//Counter - compare shadow mode

EPwm2Regs. CMPCTL. Bit. SHDWBMODE=CC_SHADOW;

EPwm2Regs. CMPCTL. Bit. LOADAMODE=CC_CTR_ZERO;//the Load registers every ZERO

EPwm2Regs. CMPCTL. Bit. LOADBMODE=CC_CTR_ZERO;

//Setup compare

//EPwm2Regs CMPA. Half. CMPA=PWM_PRD/2;

//Set the actions

EPwm2Regs. AQCTLA. Bit. CAU=0 x3;//Set PWM2A on Zero AQ_SET AQ_CLEAR

EPwm2Regs. AQCTLA. Bit. CAD=0 x3;//AQ_CLEAR AQ_SET

EPwm2Regs. AQCTLB. Bit. CAU=AQ_SET;//Set PWM2B on Zero AQ_CLEAR switch (top and bottom)

EPwm2Regs. AQCTLB. Bit. CAD=AQ_CLEAR;//AQ_SET

EALLOW;

SysCtrlRegs. PCLKCR0. Bit. TBCLKSYNC=1;//all used by enabling ePWM module synchronous TBCLK

EDIS.

////Active Low PWMs - Setup Deadband

//EPwm2Regs DBCTL. Bit. OUT_MODE=DB_FULL_ENABLE;

//EPwm2Regs DBCTL. Bit. POLSEL=DB_ACTV_HIC;

//EPwm2Regs DBCTL. Bit. IN_MODE=DBA_ALL;

//EPwm2Regs. DBRED=DEADTIME;

//EPwm2Regs. DBFED=DEADTIME;

}

CodePudding user response:

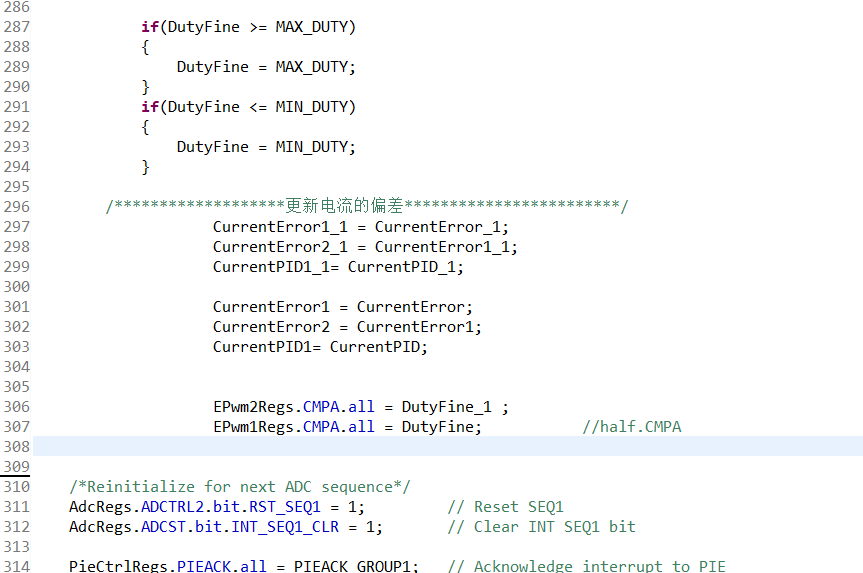

Sampling digital PID control