The results for this topic strangely all did not work.

Finally I found a variant that is logical for me and works from the same order.

CC := g

CFLAGS := -g -Wall

objects = test helloworld

all: $(objects)

$(objects): %: %.cpp

$(CC) $(CFLAGS) -o $@ $<

I have tried a lot and probably fail to fully understand the line %: %.cpp.

My interpretation is: I take from every object the dependency which in turn is based on a file which is then traceable to a .cpp file.

My theory is test expects test.o and then test.cpp.

How do I rewrite this to directory?

I have already read some things with wildcards and a pattern replace.

Like

SRC_DIR := src

OBJ_DIR := obj

SRC_FILES := $(wildcard $(SRC_DIR)/*.cpp)

OBJ_FILES := $(patsubst $(SRC_DIR)/%.cpp,$(OBJ_DIR)/%.o,$(SRC_FILES))

LDFLAGS := ...

CPPFLAGS := ...

CXXFLAGS := ...

main.exe: $(OBJ_FILES)

g $(LDFLAGS) -o $@ $^

$(OBJ_DIR)/%.o: $(SRC_DIR)/%.cpp

g $(CPPFLAGS) $(CXXFLAGS) -c -o $@ $<

But the behavior was not the expected.

When 2 cpp files were in the folder the result was

g -o helloworld.o helloworld.cpp

g -o helloworld.o test.cpp

Or vice versa that only the cpp file was always the same.

I have the feeling to miss something extremely.

Update: The make version is

GNU Make 4.3

Built for aarch64-unknown-linux-android

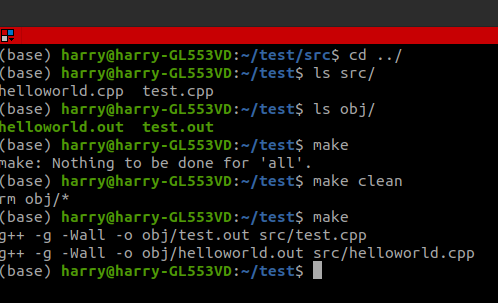

The Goal What I would like to achieve is

- src/

- Test.cpp

- Helloworld.cpp

- Obj/

Make :

- Obj/

- Helloworld.out

- Test.out

CodePudding user response:

Try this:

CXX := g

CXXFLAGS := -g -Wall

TARGETS=obj/test.out obj/helloworld.out

all:$(TARGETS)

obj/%.out:src/%.cpp

$(CXX) $(CXXFLAGS) -o $@ $^

clean:

rm obj/*