The library ieee.

Use the ieee. Std_logic_1164. All;

Use the ieee. Std_logic_arith. All;

Use the ieee. Std_logic_unsigned. All;

The entity lk_lc is

The port (CLK, LP, LR: in std_logic;

LEDL: out std_logic_vector (2 downto 0));

end;

Architecture concerns of lk_lc is

24 downto signal CNT: std_logic_vector (0);

Signal cnt_1: std_logic;

Signal cnt_2: std_logic;

Signal cnt_set: std_logic;

The begin

The process (CLK, LP, LR)

Variable count: integer range 0 to 2:=0;

The begin

If the LP='0' then

LEDL<=(others=& gt; '0');

Count:=0;

Elsif CLK 'event and CLK=' 1 'then

If cnt_set='1' then

The case count is

When 0=& gt; LEDL & lt;="001";

When 1=& gt; LEDL & lt;="010";

When 2=& gt; LEDL & lt;="100";

The when others=& gt; null;

End a case;

If the count=2 then

Count:=0;

The else count:=count + 1;

end if;

end if;

end if;

End the process.

The process (LP, CLK)

The begin

If the LP='0' then

CNT & lt;=(others=& gt; '0');

Cnt_1 & lt;='0'. Cnt_2 & lt;='0'. Cnt_set & lt;='0'.

Elsif CLK 'event and CLK=' 1 'then

If cnt_2='0' and cnt_1='1' and CNT (23)='1' then

Cnt_set & lt;='1'.

The else cnt_set & lt;='0'.

end if;

CNT & lt; CNT=+ 1; Cnt_2 & lt;=cnt_1; Cnt_1 & lt; CNT=(23);

end if;

End the process.

The end fitting concepts;

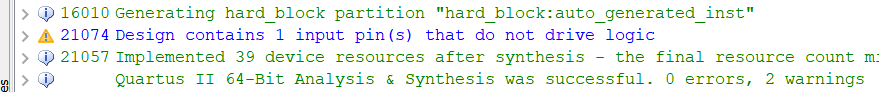

I go to baidu checked, say the clock because no drive logic count for less than, but I can change my good changed most still won't do...