After timing constraint, other violations, I have changed my good

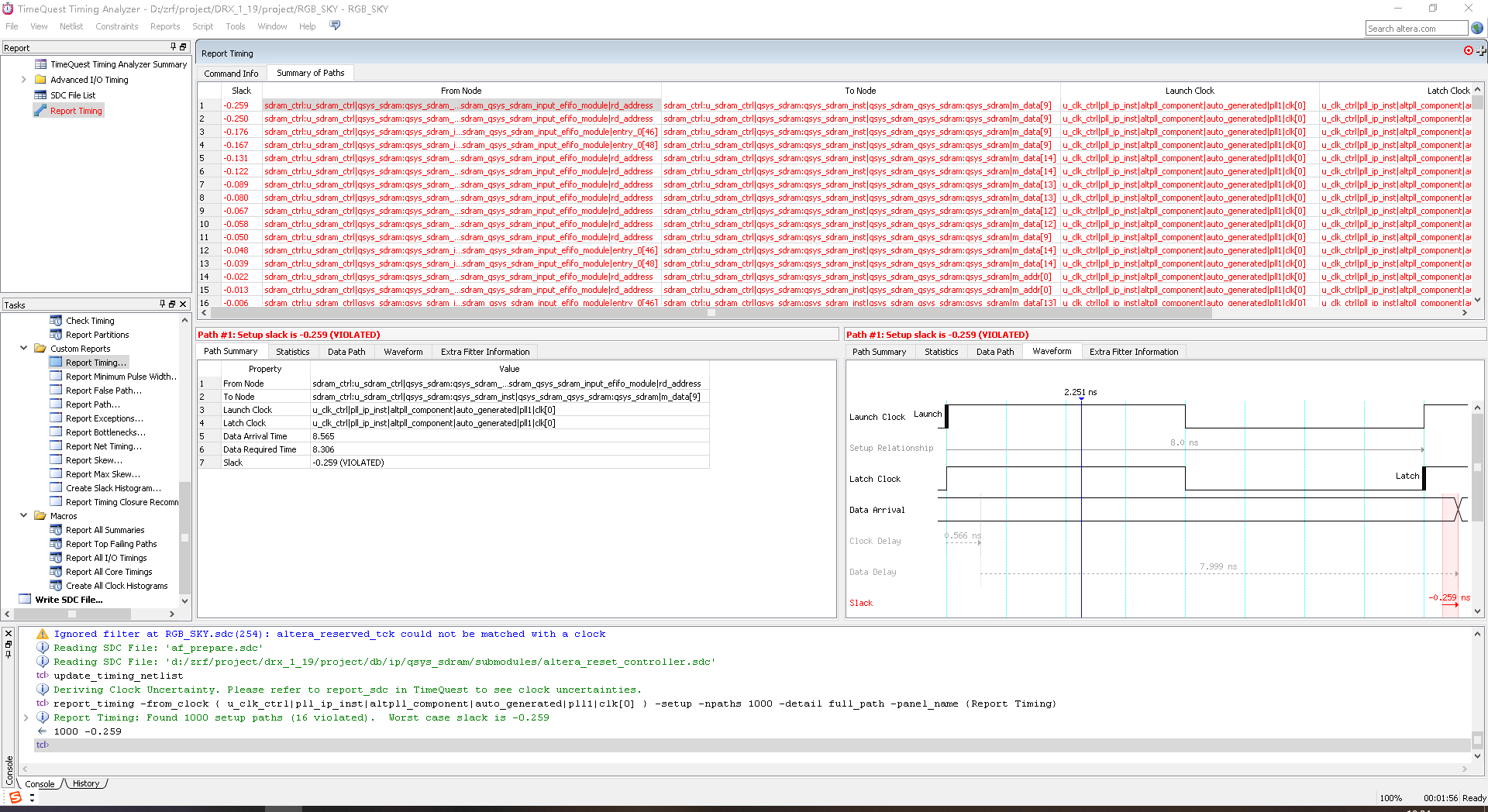

Leaves this qsys sdram internal IP violations, I don't know how to modify well,

First I put the module inside myself think the change is good, other modules are also optimized the LE about 2 k, but for the violations and nothing improve

Written in the signaltap ii look at reading and writing data, enter the data all is 0, but come out to the same address, jumping about data changes

From time to time there are data from time to time to 0, when the program is to burn-in FPGA as well, but ran after a period of time, is now a serious

Confused for a long time, because the source code is too long, bad to paste, please have encountered this kind of circumstance of bosses can give a solution, very grateful thanks,

CodePudding user response:

This module code in the https://ask.csdn.net/questions/7398542