SPI communication protocols in general need only four lines to connect main control chip and the chip, including four lines are:

(1) the SDO - the main equipment data output, data from the device to enter

(2) the SDI - master data input, data output from the device to

(3) SCLK - the clock signal, generated by the master device

(4) CS - enabling signal from the device, is controlled by a master device

Of CS is whether the control chip is selected, that is only a piece of selected signals for the prescribed enabling signal (high voltage or low potential), the operation of the chip is valid, which allows multiple SPI equipment on the same bus connection possible,

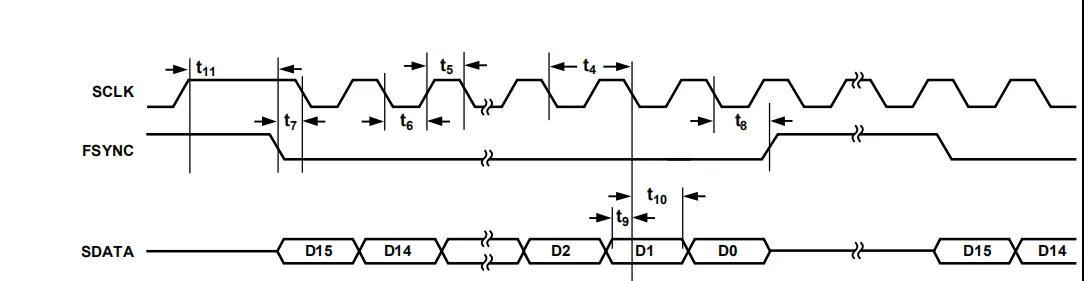

Practical application need only three lines for communication, under the SPI is serial communication protocol, the data is a a transmission, this is the reason for the existence of the SCLK the clock line, provided by the SCLK clock pulse, the SDO is based on the impulse to complete data transmission, data output through the SDO line change when the clock rising or falling edge, completed a data transmission, the input and use the same principle, at least 8 times of the clock signal change (on under and along for a), can be completed 8 bits of data (a byte data) transfer, below is the SPI communication protocol involved in the project of timing the graph is a 16-bit data,

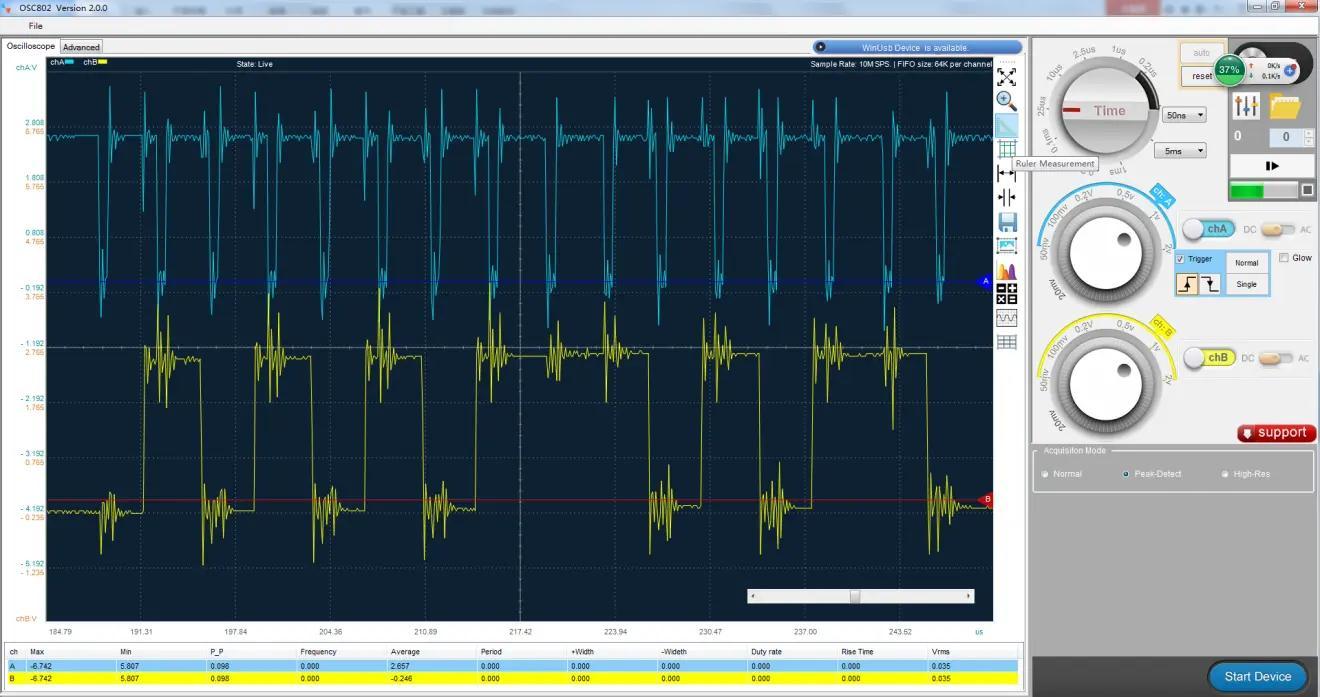

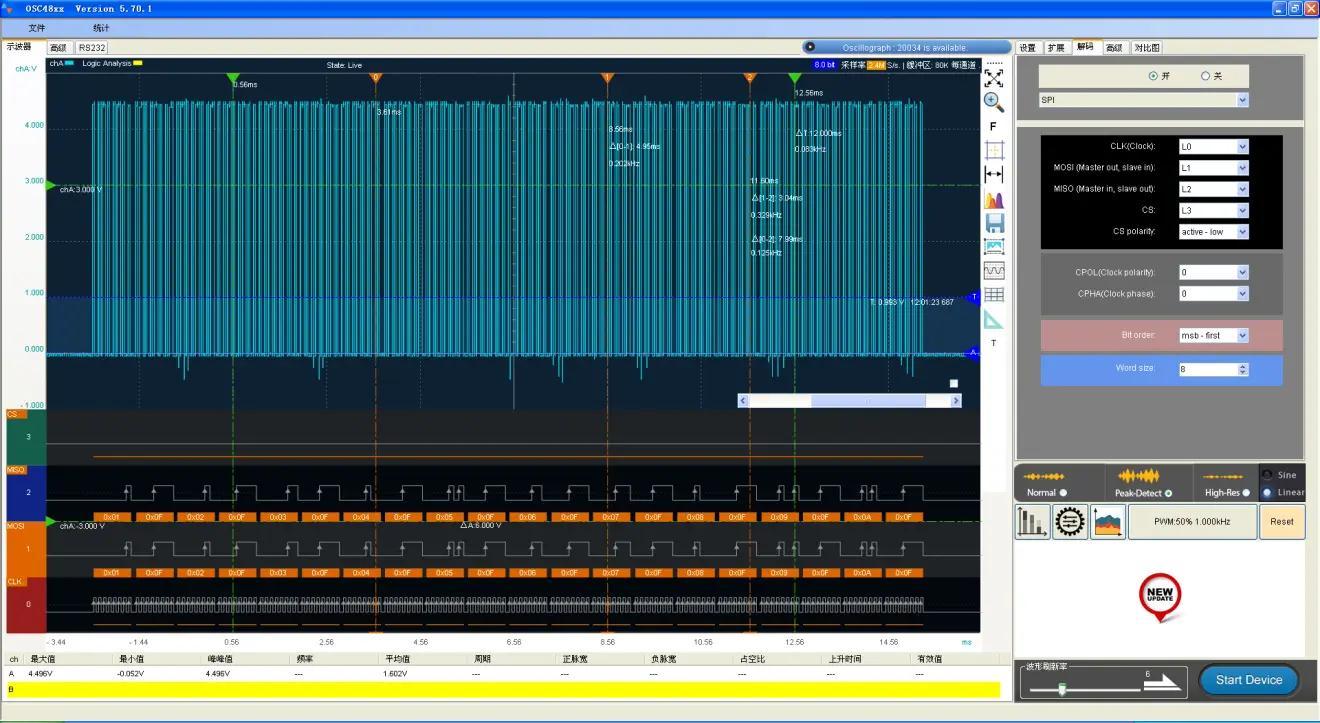

Example of this is my first attempt failed, use the USB oscilloscope OSCA02 LOTO collected corresponding waveform as shown in the figure below,

Ground wire is too long causing the signal noise is bigger, but it is the root cause of failure, I only have two input channel oscilloscope, so I can only see the main clock and data, the relation between all the way well can't decode, everyone can intuitive feelings under actual SPI signal, behind have eggs,

In a SPI based equipment, at least one master device, the characteristics of such transmission: unlike ordinary serial communication, serial communication of ordinary continuous transmitting at least 8 bits of data at a time, and a SPI allows data transmission, allowed to suspend, even when there is no clock jump, not collect or send data from the device, the master device through control of the SCLK the clock line can complete control of the communication, because of SPI data input and output line independently, so allow complete data input and output at the same time, the different ways of the realization of the SPI equipment is different, mainly change and data acquisition time is different, the clock signal on or next acquisition have different definitions,

SPI interface does not need to be addressed, and for full-duplex communication, simple and efficient, hardware is a little more complicated than the I2C system, due to the flow control SPI is not specified, no response to confirm whether to receive data,

Only in their own projects to data output mode, so the SPI serial line 3 way to communicate: a clock line SCLK, an output line of CS, a data output line SDO;

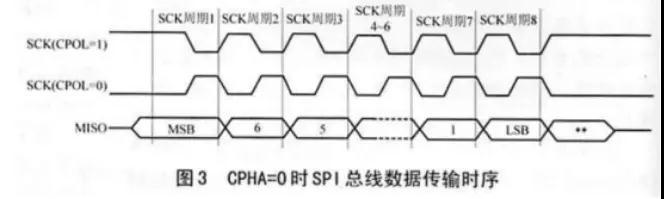

SPI module for data exchange and peripherals, its output serial synchronous clock polarity and phase can be configured, the clock polarity (CPOL) no significant impact to transport protocol, if CPOL=0, the idle state of serial synchronous clock for the low level; If CPOL=1, the idle state as the high level of serial synchronous clock, the clock phase (CPHA) can be configured to select one of the two different transport protocols for data transmission, if CPHA=0, the first jump in serial synchronous clock along (up or down) data sampling; If CPHA=1, the second jump in serial synchronous clock along (up or down) data by sampling, SPI main module and communicate with external equipment clock phase and polarity should be consistent,

Main equipment configuration of SPI interface clock to find out from the device when clock requirements, for the equipment of the clock polarity and phase are from the device as a benchmark, so on the clock polarity configuration must be clear from the device is in the rising clock or falling down the receiving data, is the falling edge of the the clock or rising along the output data,

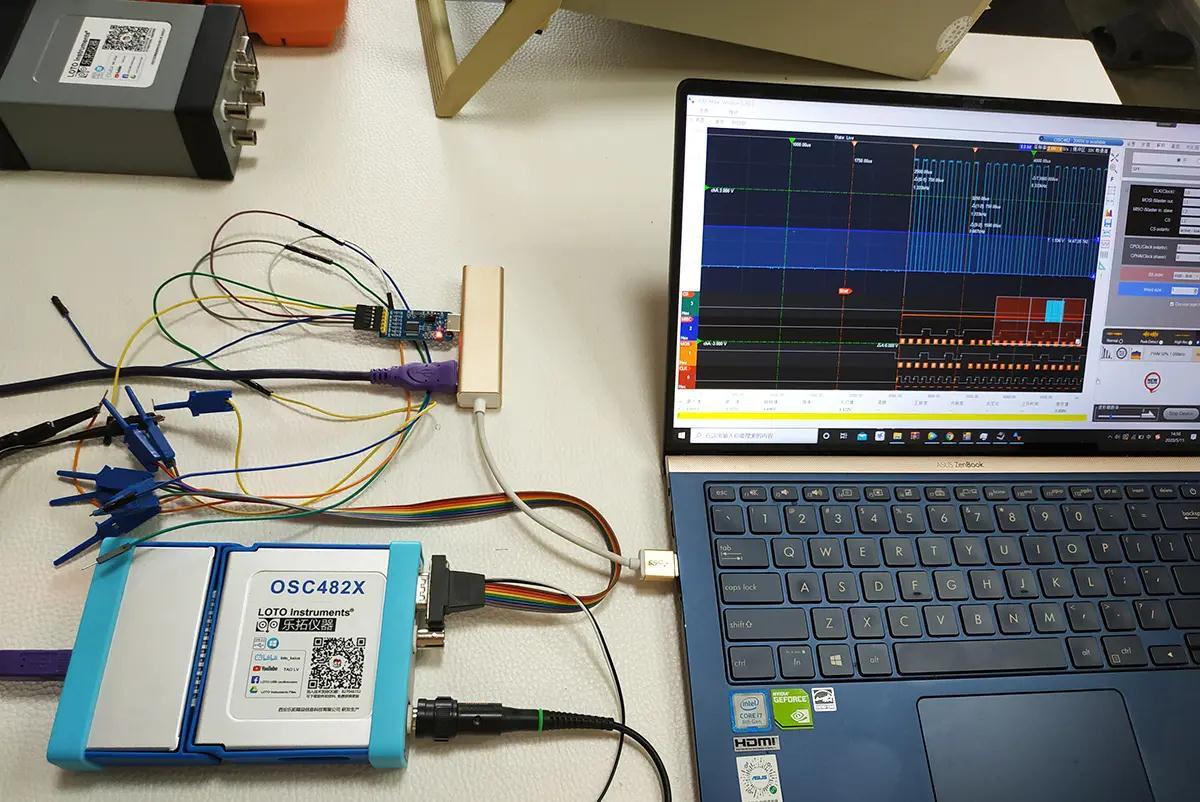

Now, I am the oscilloscope to upgrade a OSCA02L, was oscilloscope and logic analyzer is a body, so this time completely have the opportunity to do 4 line SPI and decoding,

With the basis of the above, I do this using USB virtual oscilloscope + logic analyzer SPI test and the process of decoding, filmed the video, than by more intuitive, as shown in the following:

https://www.bilibili.com/video/BV1na4y1e72c