There was a problem: the hardware debugging PC to send arp request FPGA, FPGA can receive the PC data protocol stack, but the FPGA to send arp reply and send arp request, receive a less than PC, catching the package wireshark,

Has been bound into a static IP address, 192.168.1.5 (FPGA) to192.168.1.3 (PC), tried arp -s directly, also can't,

Test, inband_link_status='1'; Inband_clock_speed="10". Inband_duplex_status='1', PHY chips have finished the negotiations, is 1000 m,

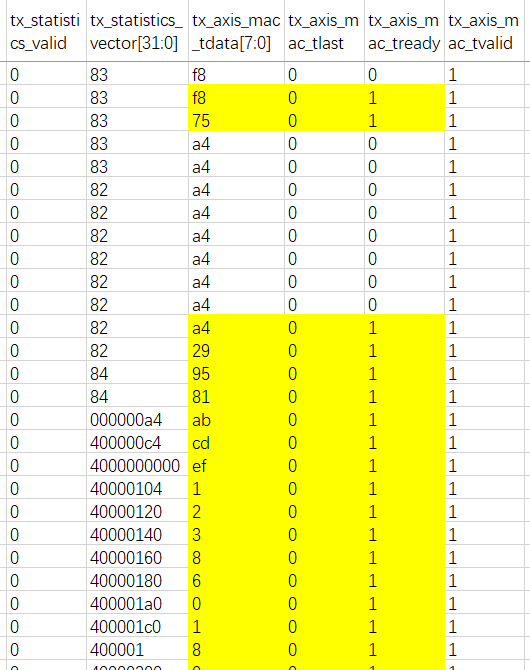

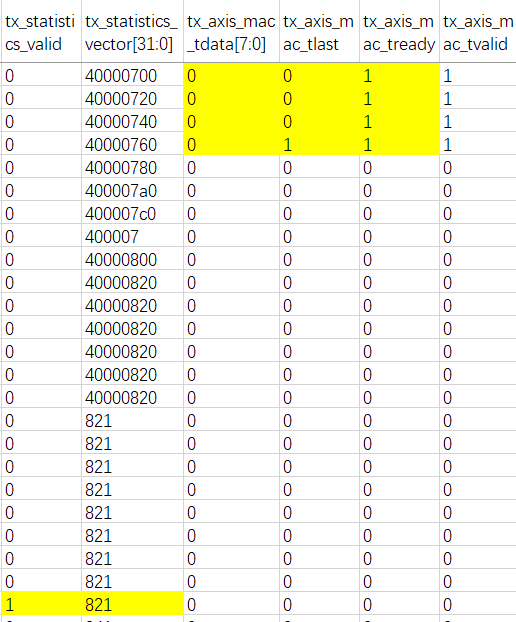

Send the data sequence and manual also 1000 m of the same; After sending data (tri mode eth MAC) IP core of tx_statistics_vector (0)='1', prove that sent MAC has completed,

I am now really don't know where have problem, why not ah, the next step debugging I don't know where to start, and, for a great god!!!!!

1) the PC firewall also had been closed, whether should also in the PC setting what ah,,,

2) (tri mode eth MAC) of the IP core speedis100 and speedis10100 two out what value is normally? MAC Speed manual corresponds to the Configuration register [12.13], can register, 12, 13 position 0, [31.30] is the rate of the identity of the ah, my output is "00", correct?

3) is my agreement is there a problem? No matter what protocol, wireshark can out a message? IP core with CRC check? Will check had been PC away?

Tx_data with fetching: