* * * * * * * * * * * * * * * * * * * * * * * * * * * * * project description * * * * * * * * * * * * * * * * * * * * * * * * * * * * *

1. Input message length 64 ~ 2048 bytes;

2. The minimum interval between the input message for two;

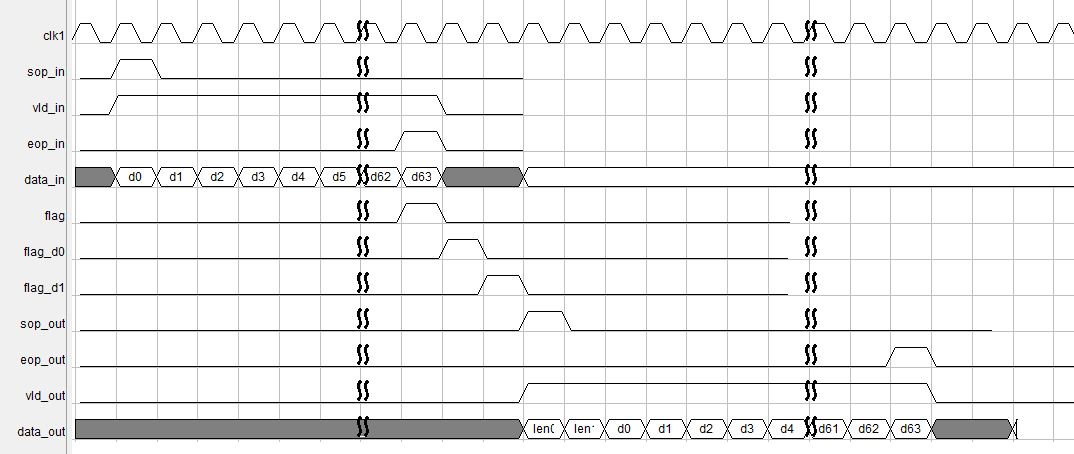

3. The output message of the first two add 16 bit packet length information;

1 for packet length high eight; 2 for low packet length 8; Take 3 starts for the input message;

* * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * *

* * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * */

The module mod_qdr (

//the system signals

Input sys_clk,

Input sys_rst_n,

//input

Input sop_in,//input message header indicating signal, high effective

Input eop_in,//input message end counter signal, high effective

Packet data input vld_in,//input signal effectively, high effective

Input [away] data_in,//input packet data

//the output

The output reg sop_out,//output message header indicating signal, high effective

The output reg eop_out,/tail/output message indicating signal, high effective

The output reg vld_out,//output packet data signal effectively, high effective

The output wire [away] data_out//output packet data

);

Reg rst_n_d0;

Reg rst_n_d1;

Reg wr_en;

Reg rd_en;

Reg [15:0] data_len;//message length

Wire [away] dout;

Wire full;

Wire the empty;

Wire almost_empty;

Wire flag;//message entry signal

Reg flag_d0;

Reg flag_d1;

The assign flag=vld_in & amp; & Eop_in;

Fifo_generator_0 u_fifo (

CLK (sys_clk),//input wire CLK

. SRST (rst_n_d1),//input wire SRST

Din (data_in),//input wire [7:0] din

. Wr_en (wr_en),//input wire wr_en

. Rd_en (rd_en),//input wire rd_en

Dout (dout),//the output wire [7:0] dout

Full (full),//the output wire full

Empty (empty),//the output wire empty

. Almost_empty (almost_empty)//the output wire almost_empty

);

//asynchronous reset, synchronous release

Always @ (posedge sys_clk or negedge sys_rst_n) begin

if(! Sys_rst_n)

Rst_n_d0 & lt;=1 'b0;

The else

Rst_n_d0 & lt;=1 'b1;

End

Always @ (posedge sys_clk or negedge sys_rst_n) begin

if(! Sys_rst_n)

Rst_n_d1 & lt;=1 'b0;

The else

Rst_n_d1 & lt;=rst_n_d0;

End

//to enter the message signal flag register two beats, used as the output moment of message length

Always @ (posedge sys_clk or negedge rst_n_d1) begin

if(! The begin rst_n_d1)

Flag_d0 & lt;=1 'b0;

Flag_d0 & lt;=1 'b0;

End

The else begin

Flag_d0 & lt;=flag;

Flag_d0 & lt;=flag_d0;

End

End

//the length of the message count

Always @ (posedge sys_clk or negedge rst_n_d1) begin

if(! Rst_n_d1)

Data_len & lt; D0=16 ';

Else if (sop_in==1 'b1 & amp; & Vld_in==1 'b1)

Data_len & lt; D1=16 ';

Else if (eop_in==1 'b1 & amp; & Vld_in==1 'b1)

Data_len & lt; D0=16 ';

Else if (vld_in==1 'b1)

Data_len & lt;=data_len + 1 'b1;

The else

Data_len & lt; D0=16 ';

End

//data_out: in the first two output message length, shoot 3 starts for the input message data

Always @ (posedge sys_clk or negedge rst_n_d1) begin

if(! Rst_n_d1)

Data_out & lt; D0=8 ';

Else if (flag_d0)

Data_out & lt;=data_len [or];

Else if (flag_d1)

Data_out & lt;=data_len [away].

The else

Data_out & lt;=dout;

End

//rd_en

Always @ (posedge sys_clk or negedge rst_n_d1) begin

if(! Rst_n_d1)

Rd_en & lt;=1 'b0;

Else if (flag_d1)

Rd_en & lt;=1 'b1;

Else if (almost_empty)

Rd_en & lt;=1 'b0;

/* else

Rd_en & lt;=rd_en;//this is no problem??

*/

End

//sop_out

Always @ (posedge sys_clk or negedge rst_n_d1) begin

if(! Rst_n_d1)

Sop_out & lt;=1 'b0;

Else if (flag_d0)

Sop_out & lt;=1 'b1;

Else if (flag_d1)

Sop_out & lt;=1 'b0;

The else

Sop_out & lt;=1 'b0;//this is no problem??

End

//eop_out

Always @ (posedge sys_clk or negedge rst_n_d1) begin

if(! Rst_n_d1)

Eop_out & lt;=1 'b0;

Else if (almost_empty)//empty signal can be used?

Eop_out & lt;=1 'b1;

Else if (empty)

Eop_out & lt;=1 'b0;

/* else

Eop_out & lt;=eop_out;//this is no problem??

*/

End

//vld_out

Always @ (posedge sys_clk or negedge rst_n_d1) begin

if(! Rst_n_d1)

Vld_out & lt;=1 'b0;

Else if (flag_d0)

Vld_out & lt;=1 'b1;

Else if (almost_empty)//almost_empty signal can be used?

Vld_out & lt;=1 'b0;

The else

Vld_out & lt;=1 'b0;

End

Endmodule

CodePudding user response: