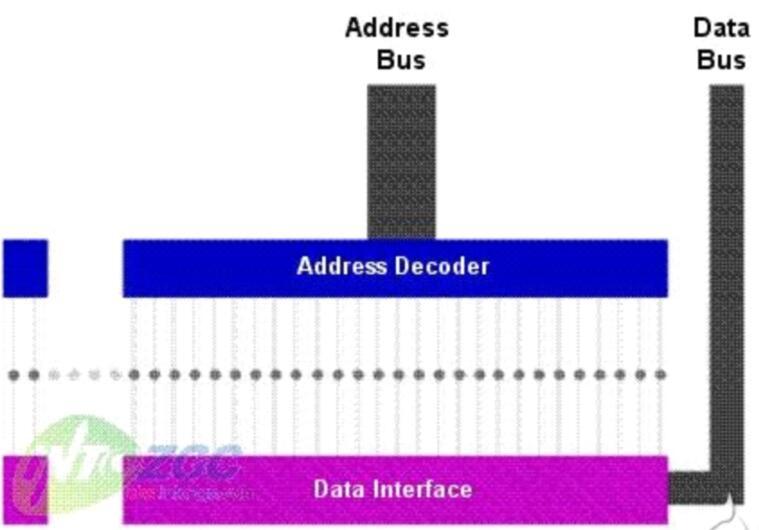

For the CPU, the RAM is like a long have a lot of Spaces of fine lines, each space has a unique address and at the same time, if the CPU wants to call data from RAM, it first is the need to send the address bus address data location to access data, and then wait for a number of clock cycles, data bus can transmit the data to the CPU, the following about SRAM memory principle diagram can help us good understanding this process,

Figure 1

Figure 1 above cited the case of CPU in a row just at a time to access a byte of data, but in the real world is different, the CPU usually every time you need to call the 32 bit or 64 bit data (this is according to the data bus of different computer systems in the determination of a wide), if the data bus is 64 bytes, the CPU can access in a time of 8 bytes of data (think of it, if every time or access to one byte of data, 64 - bit bus will not display any advantage,)

Above the small dot on behalf of the storage space in the RAM, each has a unique address line connected with it, when the address decoder to receive bus transfer to the address of the data, it will be based on the data to locate the central processor want to invoke data location, and then the data bus will send the data to the CPU,

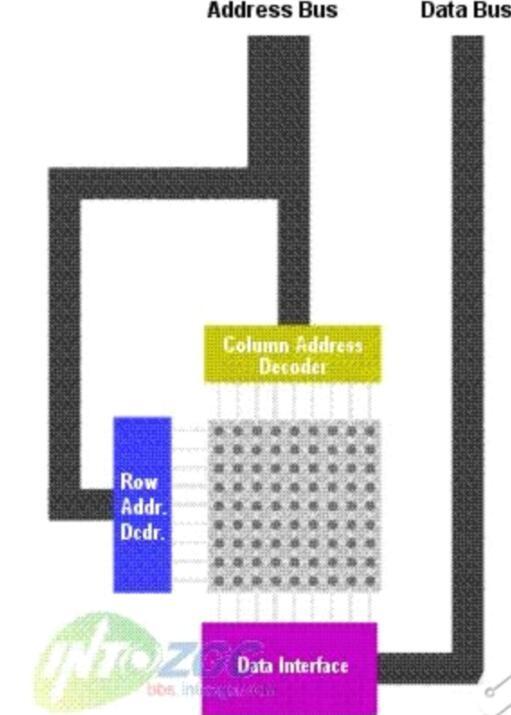

Figure 2

If the RAM for the CPU is just a "line", also cannot reflect the actual running situation, because if the situation is really so, at the time of actual manufacturing chip, there will be a lot of practical difficulties, especially in the need to design the large capacity of RAM, so a better able to reduce the cost method is to make the "space" of the information stored in the arrangement for many lines, each "Spaces" corresponding to the position of a bit storage, if you want to store 1024 bits (2 ^ 10) data, then as long as you use 32 x32 (2 ^ 2 ^ 5 * 2 ^ 5=10) matrix is able to achieve this goal, obviously a 32 x32 matrix is better than a 1024 - bit line equipment is compact, is easy to implement, see figure 2.

CodePudding user response: