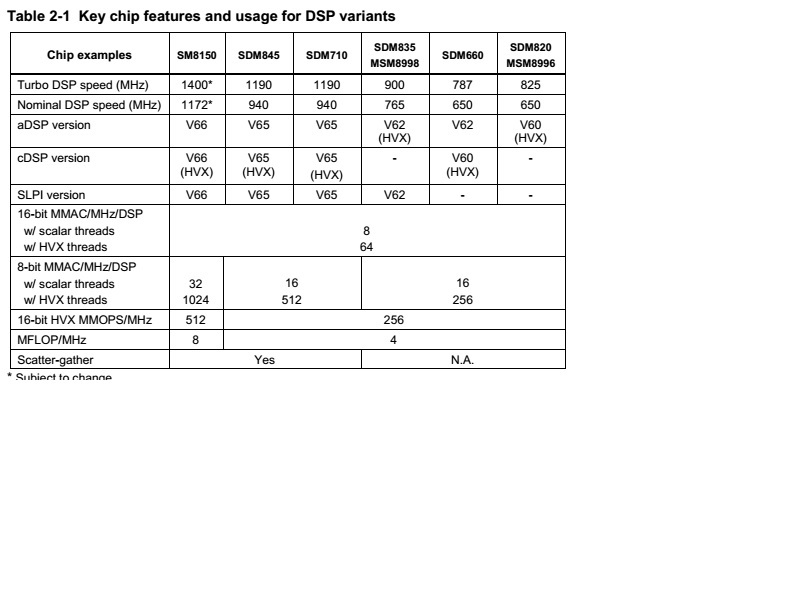

Arjun MAC/MHz/DSP with scalar threads unit=scalar MAC/cycle? Scalar vector operations, the vector is 64 bit, an instruction 4 16 bit MAC, here are 8, is two slot?

And v66 mentioned Scalar MAC and Floating Point capability is doubled, with each cluster now having its own dedicated units, so v66 should be 16?

With HVX threads as vector unit MAC/cycle, the vector is 1024 bits, 64 16 bit MAC one instruction, so also should * 2=128 and corresponding to the above, can be in here?

B.M flops/MHz=float operation cycle, support for single precision, scalar unit two float, an instruction v65 also * 2, according to two slot to, and v66 is 8, because the two culster not Shared resources

C. MOPS/MHz=op/cycle? What meaning

Two HVX d.v 65 units, v66 four HVX units, then the vector number reg * 2, * 4, and the load time and bandwidth calculate to 1024 - bit * 2102 bit 4 * 4?

E. another 16 bit SM8150 MMAC/MHz/DSP w/HVX threads is 64, but I see other documents have written above is 128??