Examples of simulation results and I why so much difference, here is the picture and the test code

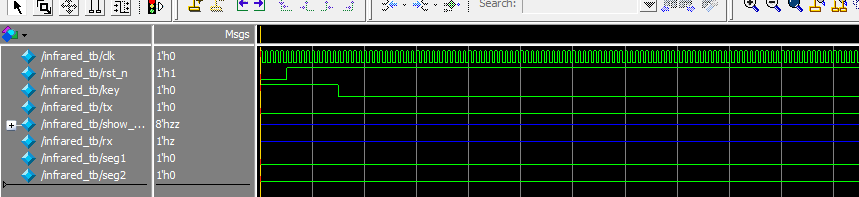

My simulation waveform

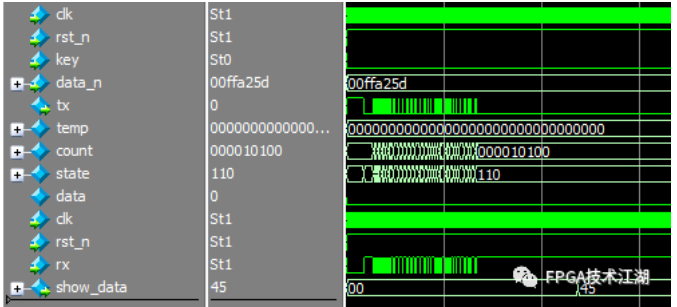

The example simulation waveform

Consult, consult

Test source:

0 ` timescale ns/1 ps

1

2 the module infrared_tb ();

3

Four reg CLK, rst_n;

5 reg key;

6 wire tx;

7 wire [away] show_data;

8

9//because we send only one data in the code, so you can pull the key has been low

10

11 initial begin

12 CLK=1;

13 rst_n=0;

14 key=1;

15

16 # 100.1 rst_n=1;

17

18 # 200 key=0;

19

20 end

21

22 always # 10 CLK=~ CLK;

23

24 infrared dut (

25. The CLK (CLK),

26. The rst_n (rst_n),

27. The key (key),

28. Tx (tx),

29. The rx (rx),

30. Seg1 (seg1),

31. Seg2 (seg2)

32);

33

34 endmodule