I use Verilog HDL description of synchronous reset circuit, why asynchronous reset circuit is integrated out?

The code is:

The module syn_reset (

Input rst_n,

The input CLK,

Input data_in,

The output out

);

Reg out;

Always @ (posedge CLK)

The begin

if(! Rst_n)

The out & lt;=1 'b0;

The else

The out & lt;=data_in;

End

Endmodule

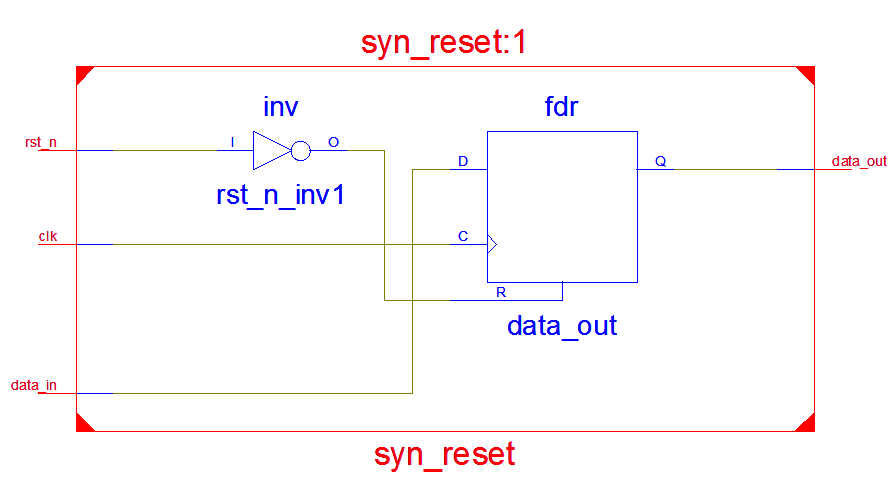

Integrated circuit for:

Thank you for your bosses to give reasonable explanation? Use the ISE integrated circuit why and I don't think the same?

CodePudding user response:

Add rst_n also to try in sensitive signal

Always @ (negedge rst_n or posedge CLK)

CodePudding user response:

Thank you for your reply, if rst_n on sensitive folders, it is not the purpose of my test, it integrated the circuit must be asynchronous, what I want is synchronous reset is not register special reset port CLR,

CodePudding user response:

reference 1st floor zgl7903 response: add rst_n also to try in sensitive signal thank you for your reply, will reset signal to join the list of sensitive, it is not the purpose of my design synchronous reset, arguably, integrated circuit diagram of should not used registers reset CodePudding user response:

The rst_n with to the data, or RSTN is to slow a beat CodePudding user response:

fog oasis reference 4 floor response: rst_n with to the data, otherwise RSTN is to slow a beat CodePudding user response:

I have a contact number? CodePudding user response:

Because of ISE some device D flip-flop comes with synchronous reset, so looks like asynchronous reset, today my teacher just said ha ha CodePudding user response:

Should make into asynchronous reset, synchronous release, CodePudding user response:

The references to the eighth floor small inn Buddha response: should make into asynchronous reset, synchronous release. CodePudding user response:

references 9/f, li bo's reply: Quote: refer to the eighth floor small inn Buddha response: should make into asynchronous reset, synchronous release. I mean, I don't support the use of synchronous reset of this style of code, it is recommended to use more asynchronous reset synchronous release code, it is easier to meet timing requirements, CodePudding user response:

1, this simple verilog synchronous reset description is correct, CodePudding user response:

references to the tenth floor small inn Buddha response: Quote: references 9/f, li bo's reply: Quote: 8 reference building small inn Buddha response: should make into asynchronous reset, synchronous release. I mean, I don't support the use of synchronous reset of this style of code, it is recommended to use more asynchronous reset synchronous release code, it is easier to meet timing requirements, CodePudding user response:

refer to 12 floor li bo's reply: Quote: reference to the tenth floor small inn Buddha response: Quote: references 9/f, li bo's reply: Quote: 8 reference building small inn Buddha response: should make into asynchronous reset, synchronous release. I mean, I don't support the use of synchronous reset of this style of code, it is recommended to use more asynchronous reset synchronous release code, it is easier to meet timing requirements,