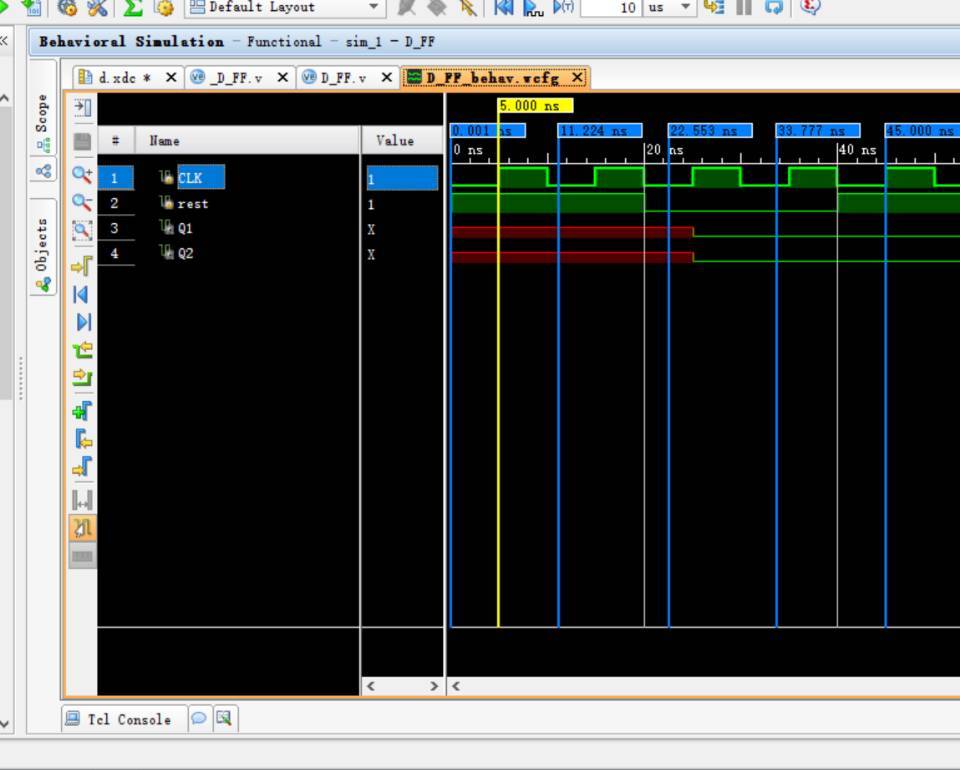

At the time of the simulation waveform graph at the beginning should not show state erratically, inquire, where write wrong!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!

The module _D_FF (

The input CLK,

Input J,

Input K,

Input RST_n,

The output reg Q1,

The output reg Q2

);

Always @ (posedge CLK)

if(! RST_n)

The begin

Q1 & lt;=0;

Q2 & lt;=0;

End

The else

Case (} {J, K)

2 'b00:

The begin

Q1 & lt;=Q1;

Q2 & lt;=Q2;

End

2 'b01:

The begin

Q1=0;

Q2=1;

End

2 'b10:

The begin

Q1=1;

Q2=0;

End

2 'bl1:

The begin

Q1 & lt;=Q2;

Q2 & lt;=Q1;

End

Endcase

Endmodule

The module D_FF ();

Reg CLK, J, K, rest;

Wire Q1 and Q2;

Always # 5 CLK=~ CLK;

Always # 20 rest=~ rest;

Initial CLK=0;

Initial rest=1;

Initial

The begin

J=0;

K=1;

End

Initial

The begin

# 5} {J, K=2 'b01;

# 17} {J, K=2 'bl1.

# 14} {J, K=2 'b00;

# 14 $stop;

End

_D_FF Asynchronous_D_FF_inst (CLK (CLK),. J (J), the K (K), the RST_n (rest), the Q1 (Q1), the Q2 (Q2));

CodePudding user response:

Cut off screen, so that can't see