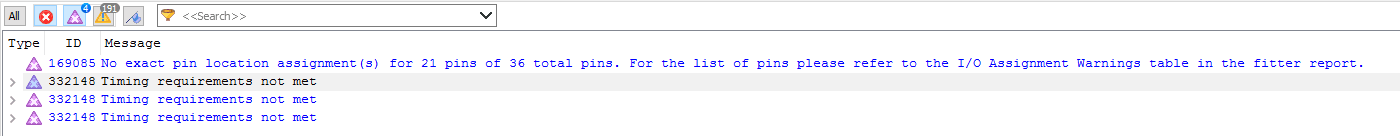

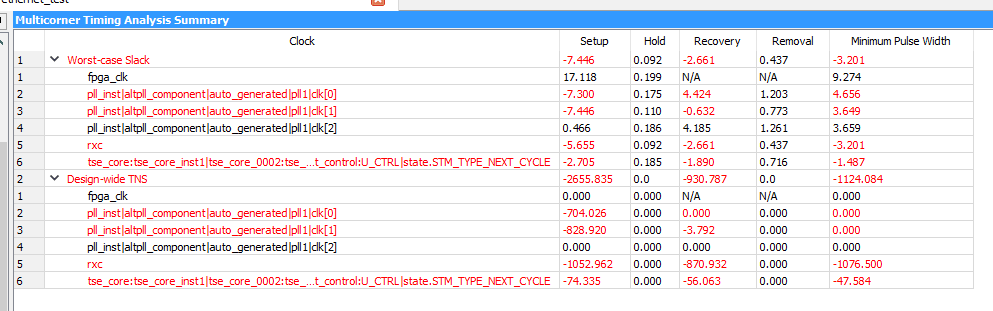

If the signaltap or SDC constraint files removed from the project, the fpga can normal communication and PC, I noticed that although can normal communication, but the compilation report have such error:

Don't know whether to join signaltap doesn't has to do with this,

CodePudding user response:

Signaltap essence, of course, is to take up the on-chip RAMCodePudding user response:

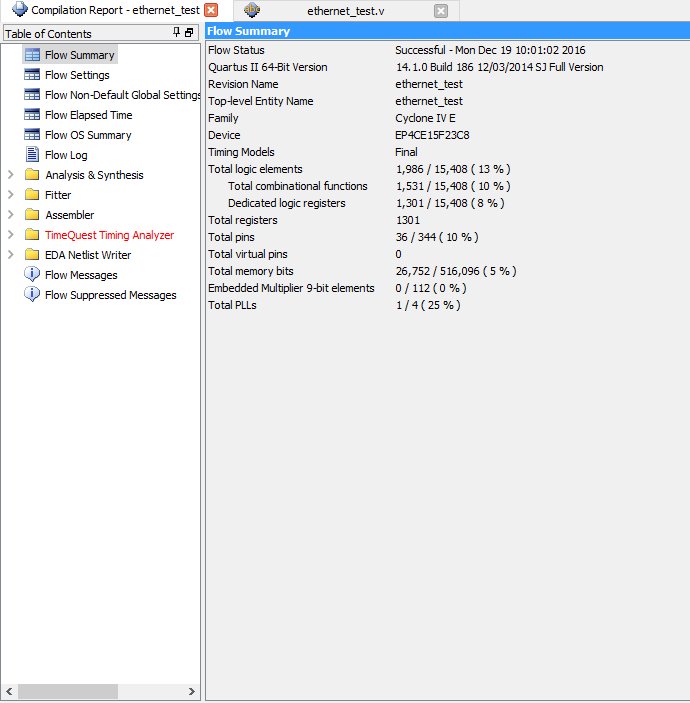

Estimated resources used by more than 70%, the first cut some modules do the signaltap catch waveform, make up and remove the signaltap module to add back, he eats much resources inside wiring is not line,CodePudding user response:

Feeling a lot of sense without signaltap inside the Total memory bits takes up to 59%, consult, in general, for Altera, in guarantee under the condition of stability, resource utilization can achieve?CodePudding user response:

Sorry, I made a mistake, as shown in figure is when I can normal communication resource usage, may not cause the condition of the resource utilization,

CodePudding user response:

Hello, the landlord to find out why? I also encountered the same problemCodePudding user response:

In general is signaltap resource-intensive problems too much, it is recommended to use external logic analyzer,CodePudding user response:

Hello, I saw your this digital phase shifter, you still have the original project can send me? (no integral) E-mail: 1157195476 @qq.comThank you for the