All the code and can refer to the specific operation steps below public number:

Part of the code is as follows:

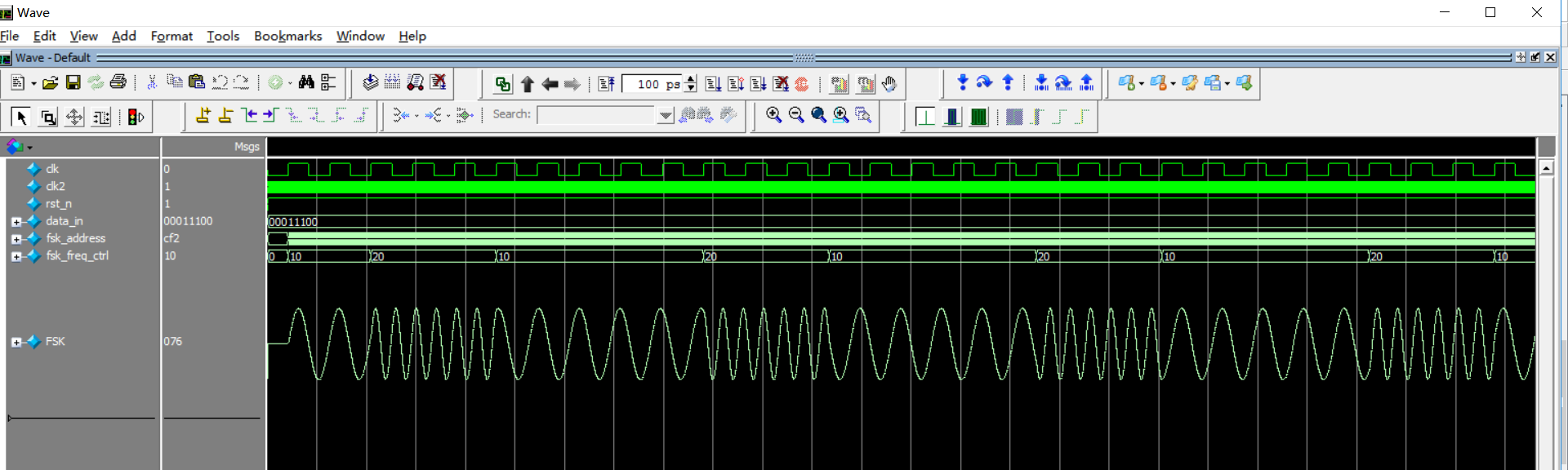

The module fsk_freq_ctrl (CLK, data_in, freq_ctrl, RST);

The input CLK.

Input [away] data_in;

Input RST.

The output/11:0 freq_ctrl;

//reg [Wednesday] q;

//parameter (I);

Reg [Wednesday] I;

Wire [Wednesday] q;

Reg [11:0] freq_ctrl;

Reg [away] a;

Always @ (posedge CLK or negedge RST)

If (RST b0)==1 '

The begin

A. & lt;=data_in;

Freq_ctrl & lt; B000000000000=12 ';

End

Else if (a [I]!=0)

The begin

Freq_ctrl & lt; D20=12 ';

End

Else if (a [I]==0)

Freq_ctrl & lt; D10=12 ';

Always @ (posedge CLK or negedge RST)

if(! RST)

I=5 'b0;

Else if (I==5 'd7)

The begin

I & lt;=5 'b0; End

Else I & lt;=I + 1;

Endmodule

//for (I=0; i<8; I=I + 1)

//if (data_in [I]==0)

//=12 'freq_ctrl d10;

//else

//=12 'freq_ctrl d20;