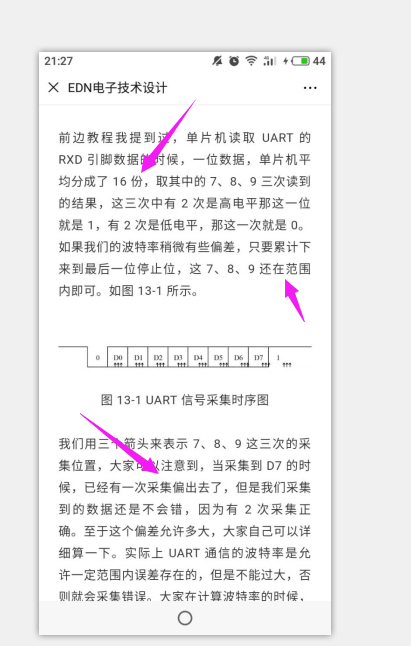

1. A data bit into 16 how understand

2.7, 8, 9 are still in the scope is to point to what mean

3. When collected when D7 once migration out how to understand? Abstract

Document links

https://mp.weixin.qq.com/s? __biz MjM5MzUxMTAwMg of===& amp; Mid=2649734149 & amp; Independence idx=2 & amp; Sn=7432806668 c934d243c54a0b9553ad52 & amp; CHKSM=be8eff3089f9762657b2cd9cca168d5c3511d0a8be5afbc4d9ff1fe7543babfc3b9a086ba207 & amp; Mpshare=1 & amp; Scene=23 & amp; Srcid=0530 # gkxqjbwbz8iibgz3mdc5 rd

CodePudding user response:

1), and the assumption 1 bit time is 16 ms, collector will once every 1 ms sampling RXD pin on the level, but only care about 7,8,9 samples values2), 1 bit length is 16 ms, but may be because the reason such as the temperature drift, cause the crystal frequency is not accurate, caused more than 16 bits of length 1 ms or less than 16 ms, only nine ms, for example, in this case, when sampling is still within the range 9,

3), due to the crystal frequency deviation, lead to actual length D7 only 8 ms, the ninth sampling, sampling to signal a stop bit, actually also is offset out

That is probably what you mean

CodePudding user response:

1. A bit is divided into 16 points can be interpreted as a bit of time (such as 9600 baud rate, a bit of time is 1/9600=104 us) sampling 16 times, thus get the data of 162. 7,8,9 also within the scope is to point to: if according to the 9600 baud rate, is about every 104 us 16 times of sampling, and the final group of 16 times in the sampling data collected by 7,8,9 data is the stop bit of data, which is within the error range,

3. This question similar to the second question, in the eighth 104 us (under normal circumstances should be D7bit) within the scope of collection, collection to the data of 16, but because the baud rate error, not 104 us a set of data, lead to the last set of data, data acquisition to the free level, the eighth data and previous data belong to D7bit, beginning from the ninth data does not belong to D7bit level, it belongs to the free level data,

Do not know to have see, didn't understand that you can continue to communication/- \

CodePudding user response:

Forget345 reply very satisfiedCodePudding user response:

Explorer _CPU, reply, and also very classic and easy to understandCodePudding user response:

16 why sampling is redundantCodePudding user response:

Anti-interference is one of the reasons, some of the work environment interference is very serious, if it's not a high sampling rate, because the number of sampling, less likely to cause misjudgment,Such as: eight times frequency, similarly take the middle three times during the time, so when the judge start bit, only need to sample first to low level 3 times,

With 16 times frequency, you may need to sample to 6 times, and the sampling interval time is shorter,

(the number of the above said would be wrong)

In addition, the general software simulation serial interface, USES is three times the frequency of sampling rate, baud rate is not high,

CodePudding user response:

@ forget345 have a few questions about1. The sample rate and the frequency doubling what relation?

2. The baud rate and the relationship between the sampling rate? Sampling rate is N times the baud rate?

3. How to understand the data width? The total time who is reading this?

4. The host and communication directly from machine what is the specific process? The host to send, receive from machine? A serial port communication, the host sends a specific what is it? What's bundle machine received? How the communication between

CodePudding user response:

@ forget345 @ explorer CPU under the two of you QQ hair bai thank youCodePudding user response:

The two of you there!