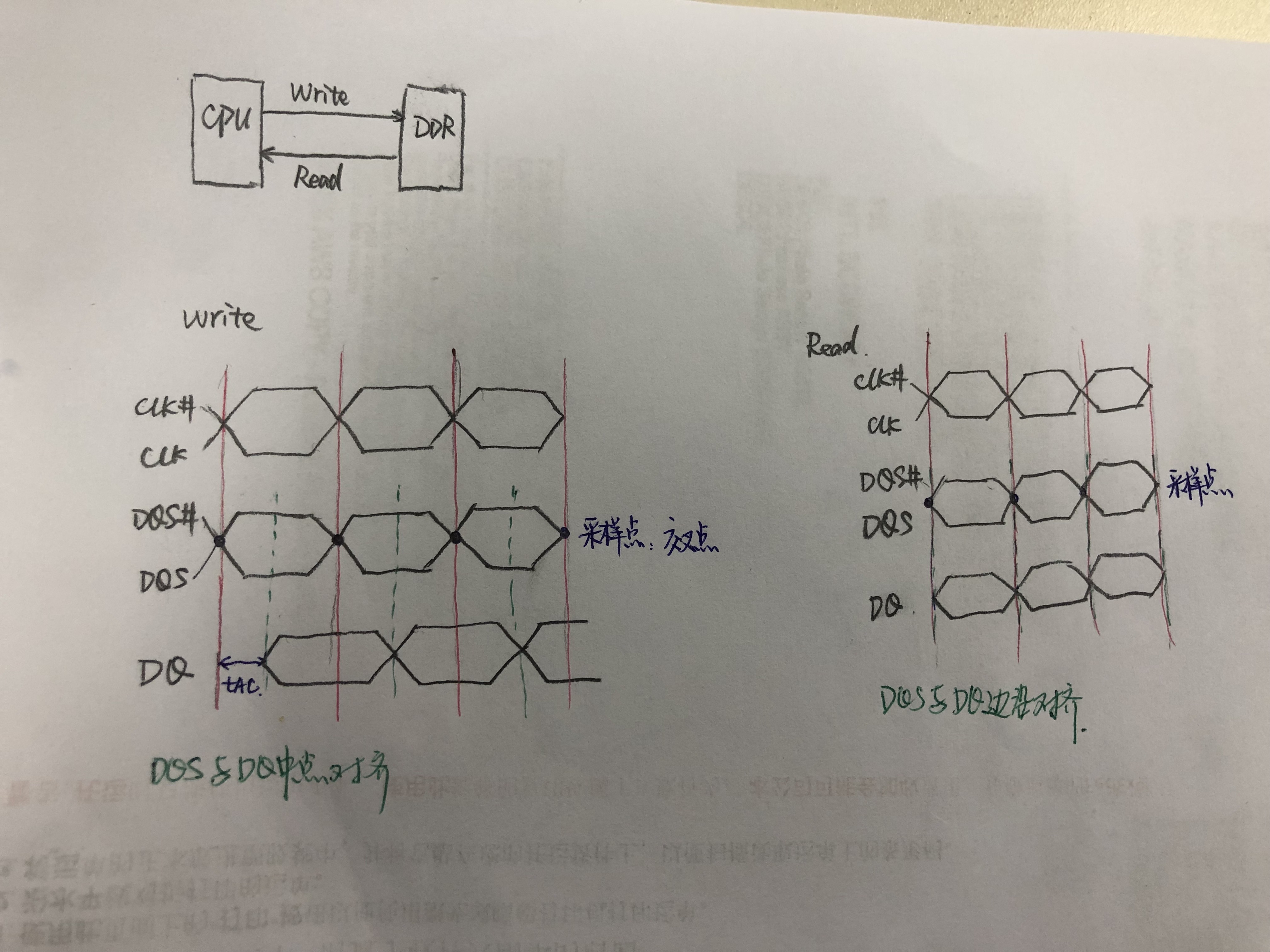

Both reading and writing, is in the DQS and DQS# crossing of sampling data? If so, write with DQ DQS route from CPU to the DDR, but as a sync signal, why the DQ and DQS delay? Really exist within the CPU suppression, in order to ensure sufficient settling time, will send DQ 1/4 cycle, prompt and DQS DQS# crossing and dairy queen in the middle of the stable level alignment, thus making the DQS with DQS# crossing sampling to stable the DQ level? But when the DDR side to send data to the CPU, and at the very edges of the crossing and DQ DQS# DQS alignment, that if it is in the DQS and DQS# crossing sampling data, how can the CPU reads to stable the right data? Sampling to see timing, feel is middle level? The great spirit guide, please!

CodePudding user response:

DDR particles inside:1. The writing is to rely on to DQS sampling DQ, so the edge in the middle of the DQ DQS is one of the best timing,

2. Read the DQS is to provide the DDR PHY to sampling DQ, usually DDR PHY will delay must tap DQS, and then used to sampling DQ