The LIBRARY IEEE.

USE the IEEE. STD_LOGIC_1164. ALL;

USE the IEEE. STD_LOGIC_ARITH. ALL;

The entity yuan_error_gen IS

The PORT (en, CLK, RST: IN STD_LOGIC;

Fairly rk, yk: SIGNED IN (7 DOWNTO 0);

Ek, ek_1 ek_2 ek_acc: OUT SIGNED 7 DOWNTO (0));

End the entity yuan_error_gen;

Architecture behaviors of yuan_error_gen is

Signal temp1: std_logic;

Signal temp2: std_logic;

Signal ek1 ek1_1, ek1_2 ek1_acc: SIGNED (7 DOWNTO 0);

The begin

Ek & lt;=ek1;

Ek_1 & lt;=ek1_1;

Ek_2 & lt;=ek1_2;

Ek_acc & lt;=ek1_acc;

The PROCESS (en, temp2)

The BEGIN

IF (en 'EVENT AND en=' 1 ') THEN

Temp1 & lt;='1'.

IF (temp2='0') THEN

Temp1 & lt;='0'.

END IF;

END IF;

END the PROCESS.

The PROCESS (CLK, temp1, RST)

The BEGIN

IF (CLK 'EVENT AND CLK=' 1 ') THEN

IF (RST='1') THEN

Temp2 & lt;='1'.

Ek1 & lt;="00000000";

Ek1_1 & lt;="00000000";

Ek1_2 & lt;="00000000";

Ek1_acc & lt;="00000000";

ELSIF (temp1='1') THEN

Temp2 & lt;='1'.

Ek1 & lt;=fairly rk - yk;

Ek1_1 & lt;=ek1;

Ek1_2 & lt;=ek1_1;

Ek1_acc & lt;=+ + ek1_2 ek1_1 ek1;

Temp2 & lt;='0'.

END IF;

END IF;

END the PROCESS.

End behaviors;

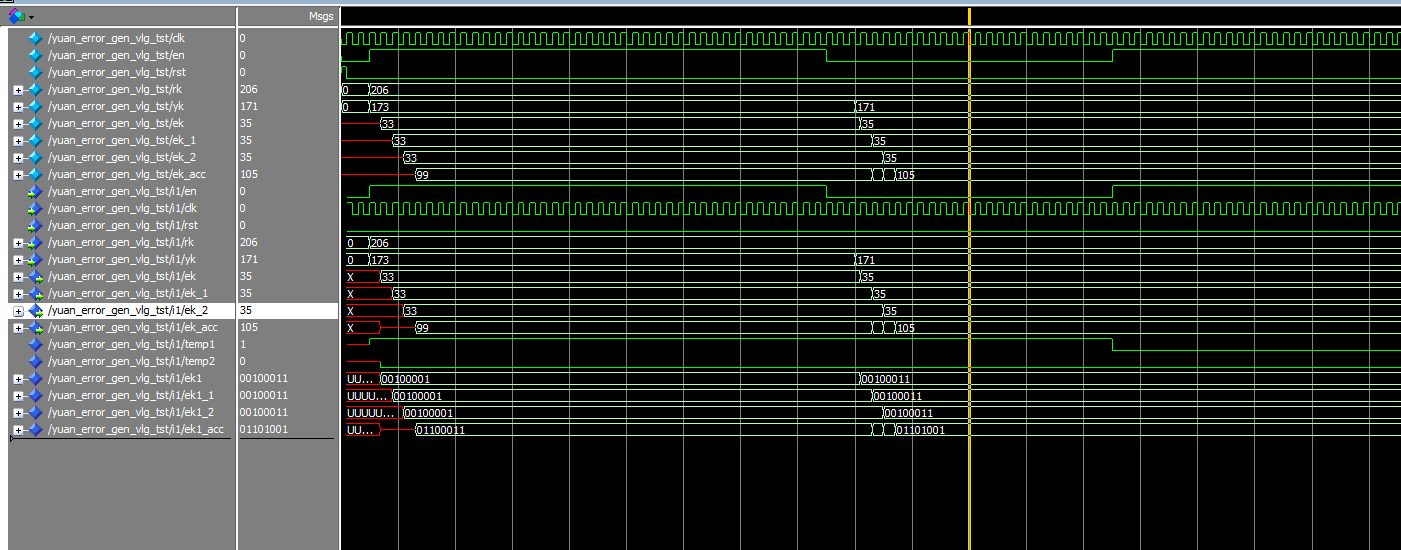

But I don't see eye to the results of the simulation, total felling the code where there is a problem, but don't know how to change, can't get where is the problem, a great god teach

The following is my modelsim simulation results