2. The power of the tested several key and the clock signal contrast,

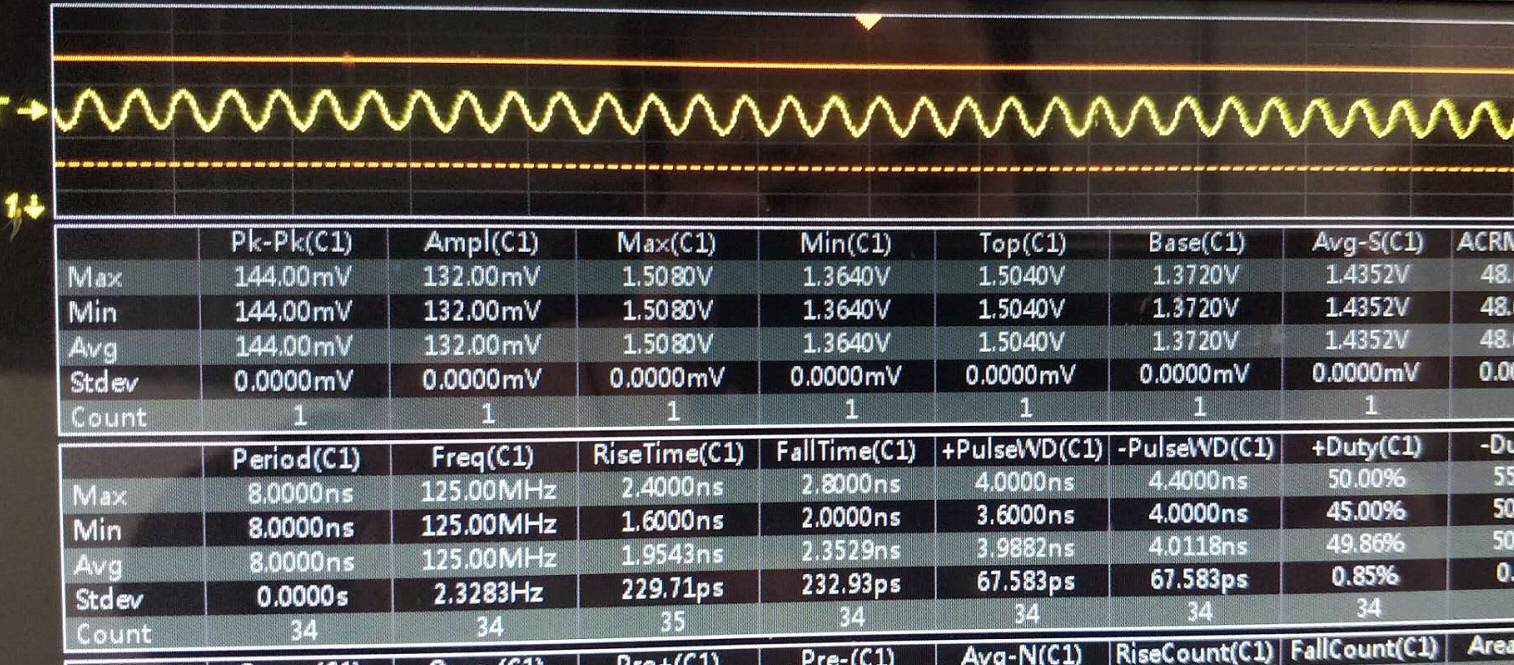

1. MAC_CLK: 125 m

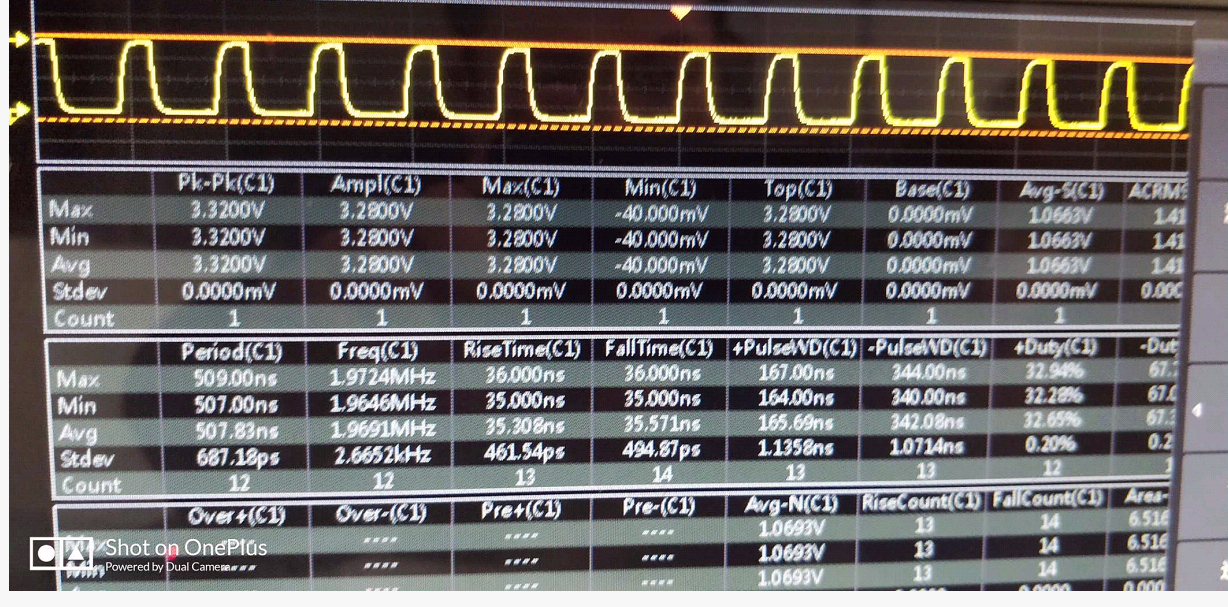

2. REGOUT output voltage of the end:

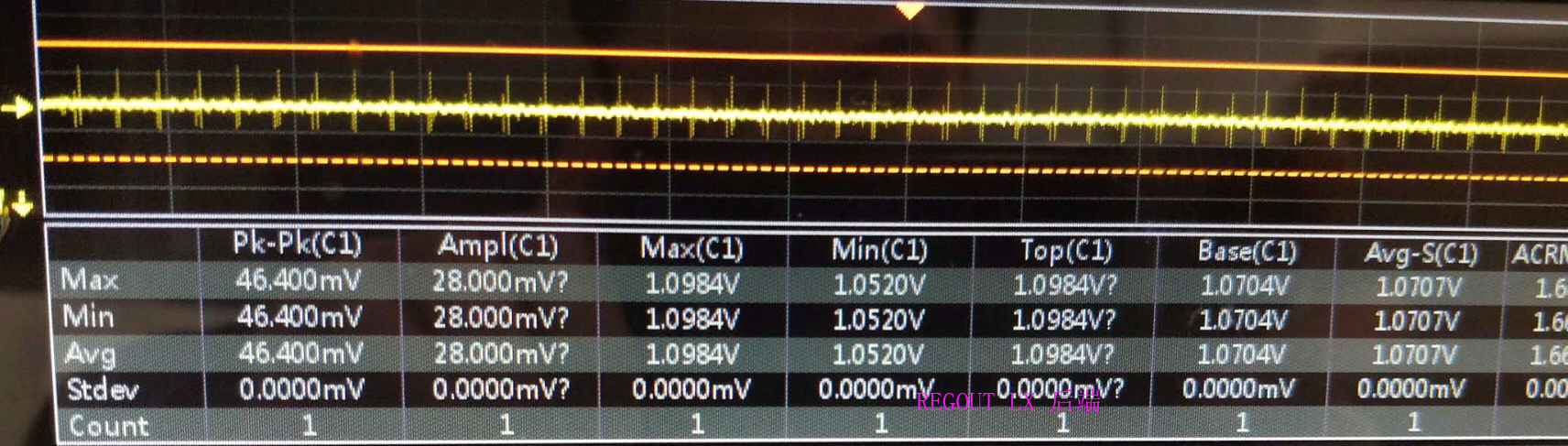

3. After 2.2 uH inductance REGOUT output power:

official does not exceed the maximum voltage range is 1.05 V of 1.09 V power supply voltage of 1.05 test development board, I design the board output on the high side, do not know whether here to gigabit transmission,

The remaining RXL CLK: 25 m hz and tx CLK: 125 MHZ output is normal, insert the cable becomes TXCLK will test after 25 MHZ.

Are the address

http://www.t-firefly.com/product/rocrk3328cc.html

CodePudding user response:

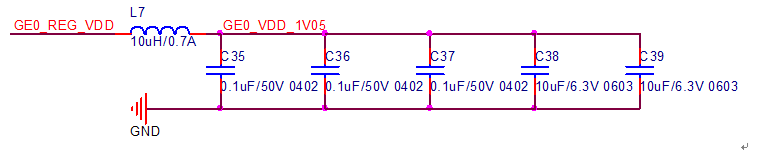

Advice note 1.05 V power supply, the building Lord inductance can be changed to 10 uh, grounding capacitance can add a few more, under the power supply noise measurement, the voltage amplitude according to the requirements, the voltage quality will affect the problem of packet loss and so on,

CodePudding user response:

Transcribe completely design official at present, the 1.05 v, you can see my wave, on the high side, is inductor and filter capacitor yo a lot to do with this?CodePudding user response:

You simply copy the DEMO board schematic diagram, layout, too? , the size of the capacitor will affect, I demonstrated that accords with a requirement to ensure that the hardware signal, then check the softwareCodePudding user response:

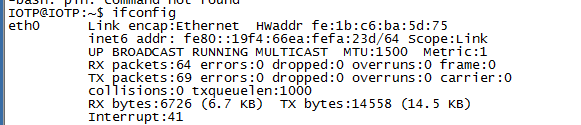

The attention of the design of the power supply point I have come up in accordance with the datasheet, design power supply problem has been encountered for the first time, so that the design focus attention to this point, but I feel a little strange, my REGOUT is stable in 1.07 V output ripple in dozens of MV. Officials stated above the highest power is 1.09 V, 1.05 the influence is very big, I again to add some capacitance, the official without PCB fileThis is the ifconfig return value, is a data transmission on the data, and

CodePudding user response:

Measuring a front-end ports eye diagram to see, no problem, should be a software problem