Problem is, I use 10 m sampling clock, the output is 8 bits, then the corresponding output data rate should be 80 m, a clock is 40 m, frame clock is 10 m, and I to electricity, with a sampling oscilloscope, found that a clock and frame clock is no problem, and the data output rate is wrong, the output output is 10 m, so obviously the sampling does not seem to be successful, for the great god what is this? Urgent ~ ~ ~ ~ jianghu tangle

CodePudding user response:

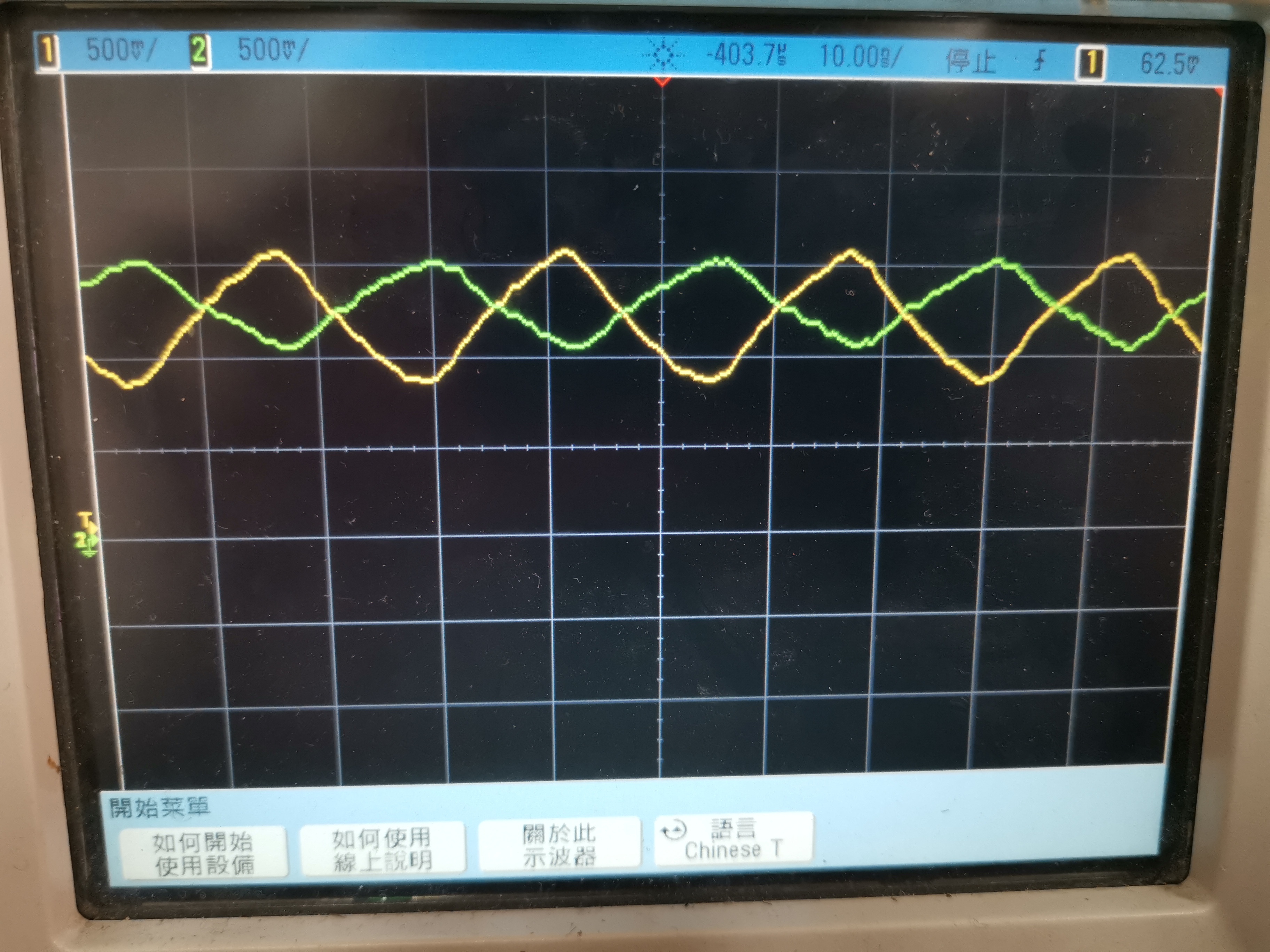

This is a clock waveform

CodePudding user response:

this is frame clock waveform

this is frame clock waveformCodePudding user response:

this is sampling clock waveform

this is sampling clock waveformCodePudding user response:

Like the output has been a constant valueCodePudding user response:

So the test data, and you must be 10 m, it is 10 m clock, skewer into the FPGA is 80 m,CodePudding user response:

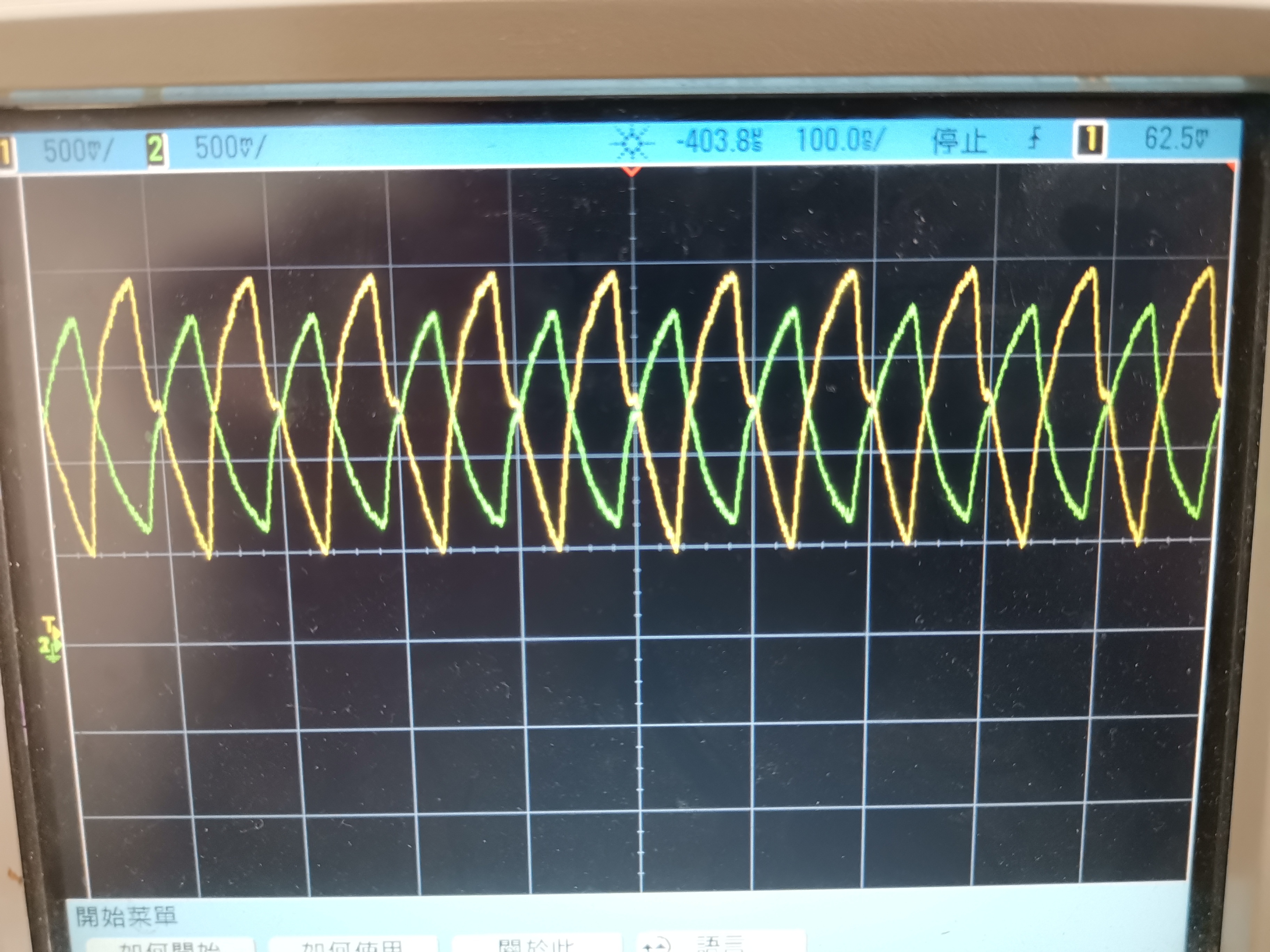

this is an LVDS data output waveform

this is an LVDS data output waveformCodePudding user response:

This is a serial an LVDS, should be output to 80 m, I seem to find the reason, chip agent sold me is 9287 BCPZ, what I need is 9287 abcpz, new chip is put on, try come back,CodePudding user response: