The module FSM_Welcome (

CLK,

Rst_n,

Data,

Start,

Num

);

The input CLK.

Input rst_n;

Input [away] data;

Input the start;//enabled signal

The output reg [2-0] num;//need to detect the sequence of the number of occurrences of the

Reg [3-0] state;

Localparam

Check_W d1,//W=4 '

Check_e0=4 'd2,//testing first e

Check_l d3,//l=4 '

Check_c=4 'd4,//c

Check_o d5,//detection o=4 '

Check_m d6,//testing m=4 '

Check_e1=4 'd7.//test the second e

Always @ (posedge CLK or negedge rst_n)

if(! Rst_n)

The begin

The state & lt;=check_W;

Num & lt; D0=3 ';

End

Else if (start)

The begin

Case (state)

Check_W: begin

If (data="W" https://bbs.csdn.net/topics/=

The state & lt;=check_e0;

The else

The state & lt;=check_W;

End

Check_e0: begin

If (data="e" https://bbs.csdn.net/topics/=

The state & lt;=check_l;

Else if (state=="W")

The state & lt;=check_e0;

The else

The state & lt;=check_W;

End

Check_l: begin

If (data="l" https://bbs.csdn.net/topics/=

The state & lt;=check_c;

Else if (state=="W")

The state & lt;=check_e0;

The else

The state & lt;=check_W;

End

Check_c: begin

If (data="c" https://bbs.csdn.net/topics/=

The state & lt;=check_o;

Else if (state=="W")

The state & lt;=check_e0;

The else

The state & lt;=check_W;

End

Check_o: begin

If (data="o" https://bbs.csdn.net/topics/=

The state & lt;=check_m;

Else if (state=="W")

The state & lt;=check_e0;

The else

The state & lt;=check_W;

End

Check_m: begin

If (data="m" https://bbs.csdn.net/topics/=

The state & lt;=check_e1;

Else if (state=="W")

The state & lt;=check_e0;

The else

The state & lt;=check_W;

End

Check_e1: begin

If (data="e" https://bbs.csdn.net/topics/=

The begin

The state & lt;=check_W;

Num & lt; D1=num + 1 ';

End

Else if (state=="W")

The state & lt;=check_e0;

The else

The state & lt;=check_W;

End

Default: state & lt;=check_W;

Endcase

End

Endmodule

2. The test file

` timescale ns/1 ns

` define clk_period 20

The module FSM_Welcome_tb;

Reg the CLK.

Reg rst_n;

Wire [away] data;

Reg the start;

Wire [2-0] num;

//wire flag;

Wire [511:0] data_tmp;

Reg [511:0] data_reg;

The assign data_tmp="abcdeWelcomehijkWelcomedcba";

Always @ (posedge CLK or negedge rst_n)

if(! Rst_n)

Data_reg & lt;=0;

Else if (start)

Data_reg & lt;=data_reg & lt; <8;

The else

Data_reg & lt;=data_tmp;

The assign data=https://bbs.csdn.net/topics/data_reg (511-504);

FSM_Welcome FSM_Welcome (CLK (CLK), the rst_n (rst_n), the data (data), the start (start), the num (num));

Initial CLK=1;

Always# (` clk_period/2) CLK=~ CLK;

Initial the begin

Rst_n=0;

Start=0;

# (` clk_period * 20)

Rst_n=1;

# (` clk_period * 10)

Start=1;

# (` clk_period * 64)

# 200;

$stop;

End

Endmodule

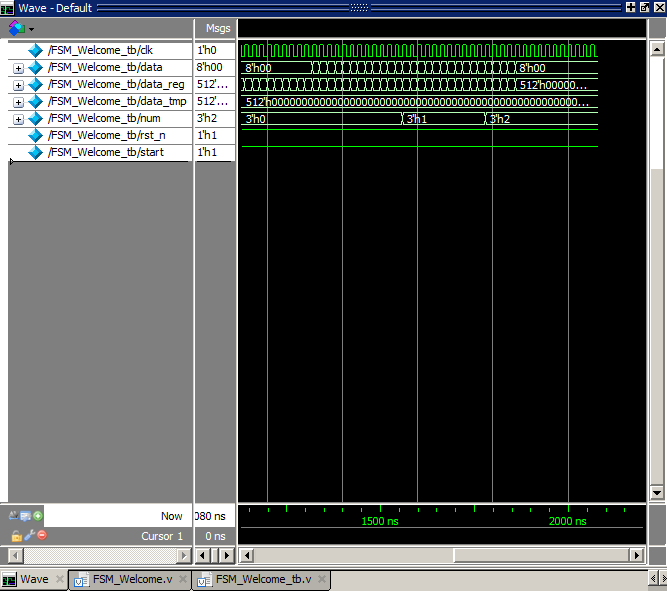

3. No waveform

CodePudding user response:

Advice to see this article: https://wenku.baidu.com/view/cd93f34ecf84b9d528ea7a95.html

https://wenku.baidu.com/view/cd93f34ecf84b9d528ea7a95.html