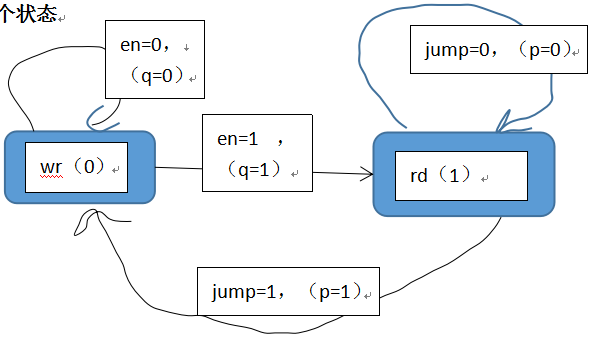

(1) one (temporal logic)

Source://state control signal generated by counter count

Always @ (posedge CLK or negedge rst_n)

if(! Rst_n) begin

CNT & lt; D0=5 ';

Ed & lt;=1 'b0;

Jump & lt;=1 'b0;

End

Else if (CNT==5 'd10) begin

Ed & lt;=1 'b1;

CNT & lt; CNT=+ 1 'b1;

End

Else if (CNT==5 'd20) begin

Jump & lt;=1 'b1;

CNT & lt; D0=5 ';

End

The else begin

CNT & lt; CNT=+ 1 'b1;

Ed & lt;=1 'b0;

Jump & lt;=1 'b0;

End

The state machine//one

Always @ (posedge CLK or negedge rst_n)

if(! Rst_n) begin

The state & lt;=wr;

p <=1 'b0;

Q & lt;=1 'b0;

End

The else begin

Case (state)

Wr: begin

If the begin (Ed)

The state & lt;=rd;

Q & lt;=1;

End

The else begin

The state & lt;=wr;

Q & lt;=0;

End

End

Rd: begin

If (jump) begin

The state & lt;=wr;

p <=1;

End

The else begin

The state & lt;=rd;

p <=0;

End

End

Endcase

End

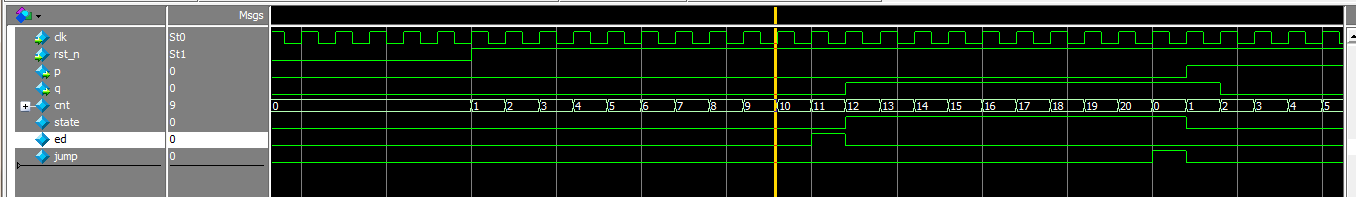

Waveform graph:

Analytic: when the counter plan to 10, Ed signal not immediately into 1, needs to wait for the next clock rise along comes to become 1; When Ed signals into 1, the state is not immediately go to the next state, also need to wait for the next clock rise along, when the state from 0 to 1, followed by q also become 1, because the code the bidding is yellow the two order, almost no delay,

(2) one (combinational logic)

Source://counter and Ed, jump assignment

The assign Ed=(CNT==5 'd10)? B1:1 '1' b0;

The assign jump=(CNT==5 'd20)? B1:1 '1' b0;

Always @ (posedge CLK or negedge rst_n)

if(! Rst_n)

CNT & lt; D0=5 ';

Else if (CNT==5 'd20)

CNT & lt; D0=5 ';

The else

CNT & lt; CNT=+ 1 'b1;

The state machine//one

Always @ (posedge CLK or negedge rst_n)

if(! Rst_n) begin

The state & lt;=wr;

p <=1 'b0;

Q & lt;=1 'b0;

End

The else begin

Case (state)

Wr: begin

If the begin (Ed)

The state & lt;=rd;

Q & lt;=1;

End

The else begin

The state & lt;=wr;

Q & lt;=0;

End

End

Rd: begin

If (jump) begin

The state & lt;=wr;

p <=1;

End

The else begin

The state & lt;=rd;

p <=0;

End

End

Endcase

End

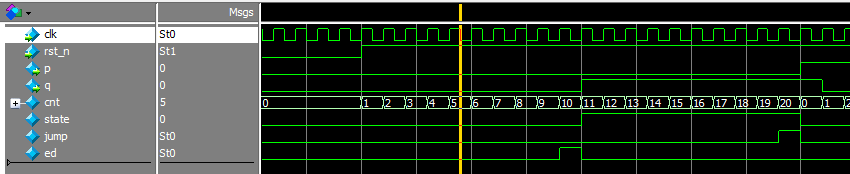

Waveform graph:

Analytic: when the counter plan to 10, because of the combinational logic assignment (non-blocking assignment) do not need to wait for the clock rising edge, so when the counter meter to the 10, Ed immediately turned into a 1 signal, when Ed signals into 1, the state is not immediately turn to the next state, also need to wait for the next clock rise along, when the state from 0 to 1, followed by q also become 1, because the code the bidding is yellow the two order, almost no delay,

(3) 3 (the third section case (n_state))

Source://counter and Ed, jump assignment

Always @ (posedge CLK or negedge rst_n)

if(! Rst_n) begin

CNT & lt; D0=5 ';

Ed & lt;=1 'b0;

Jump & lt;=1 'b0;

End

Else if (CNT==5 'd10) begin

Ed & lt;=1 'b1;

CNT & lt; CNT=+ 1 'b1;

End

Else if (CNT==5 'd20) begin

Jump & lt;=1 'b1;

CNT & lt; D0=5 ';

End

The else begin

CNT & lt; CNT=+ 1 'b1;

Ed & lt;=1 'b0;

Jump & lt;=1 'b0;

End

//the first paragraph (to c_state assignment)

Always @ (posedge CLK or negedge rst_n)

if(! Rst_n)

C_state & lt;=wr;

The else

C_state & lt;=n_state;

//the second paragraph (combinational logic, and assign n_state)

Always @ (*)

Case (c_state)

Wr:

If (Ed)

N_state & lt;=rd;

The else

N_state & lt;=wr;

Rd:

If (jump)

N_state & lt;=wr;

The else

N_state & lt;=rd;

Endcase

//the third paragraph assignment (p, q)

Always @ (posedge CLK or negedge rst_n)

if(! Rst_n) begin

p <=1 'b0;

Q & lt;=1 'b0;

End

The else begin

Case (n_state)

Wr:

If (Ed)

p <=1;

The else

p <=0;

Rd:

If (jump)

Q & lt;=1;

The else

Q & lt;=0;

Endcase

End

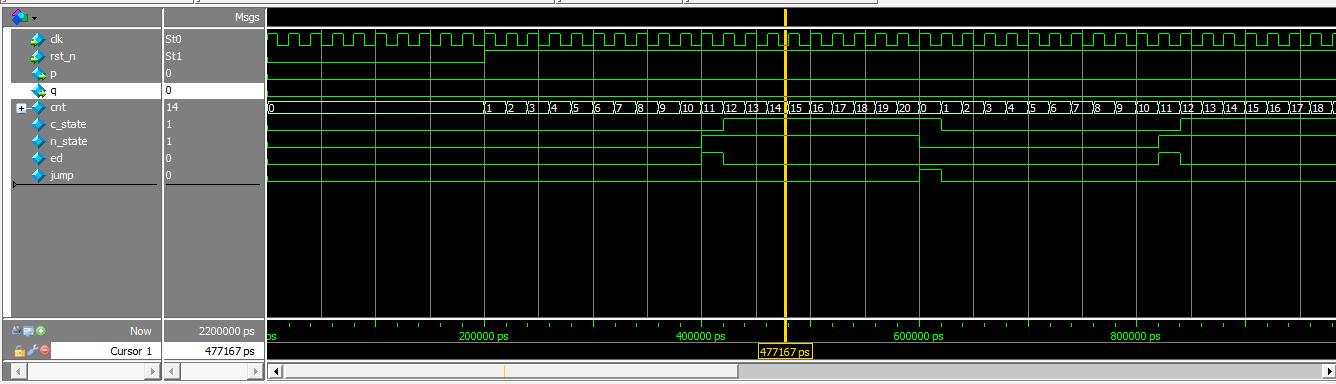

Waveform graph:

Analytic: when the counter plan to 10, Ed signal not immediately into 1, needs to wait for the next clock rise along comes to become 1; When Ed signals into 1 state because of the second paragraph is the combinational logic, so n_state immediately into the next state 1; But the first paragraph is temporal logic, so c_state needs to wait for the next clock along will change for the next state; Because the case is in the third paragraph (n_state), so when Ed signals into 1 n_state has become a rd (1) state, changing conditions is not satisfied, so q

(4) a three-stage case (the third paragraph case (c_state))

Source://counter and Ed, jump assignment

Always @ (posedge CLK or negedge rst_n)

if(! Rst_n) begin

CNT & lt; D0=5 ';

Ed & lt;=1 'b0;

Jump & lt;=1 'b0;

End

Else if (CNT==5 'd10) begin

Ed & lt;=1 'b1;

CNT & lt; CNT=+ 1 'b1;

End

Else if (CNT==5 'd20) begin

Jump & lt;=1 'b1;

CNT & lt; D0=5 ';

End

The else begin

CNT & lt; CNT=+ 1 'b1;

Ed & lt;=1 'b0;

Jump & lt;=1 'b0;

End

//the first paragraph (to c_state assignment)

Always @ (posedge CLK or negedge rst_n)

if(! Rst_n)

C_state & lt;=wr;

The else

C_state & lt;=n_state;

//the second paragraph (combinational logic, and assign n_state)

Always @ (*)

Case (c_state)

Wr:

If (Ed)

N_state & lt;=rd;

The else

N_state & lt;=wr;

Rd:

If (jump)

N_state & lt;=wr;

The else

N_state & lt;=rd;

Endcase

//the third paragraph assignment (p, q)

Always @ (posedge CLK or negedge rst_n)

if(! Rst_n) begin

p <=1 'b0;

Q & lt;=1 'b0;

End

The else begin

Case (c_state)

Wr:

If (Ed)

p <=1;

The else

p <=0;

Rd:

If (jump)

Q & lt;=1;

The else

Q & lt;=0;

Endcase

End

nullnullnull