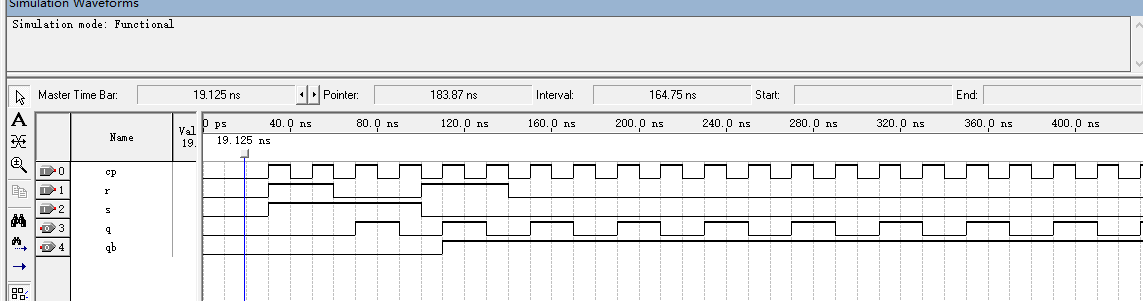

The simulation diagram:

Code:

The library ieee.

Use the ieee. Std_logic_1164. All;

The entity r_s is

The port (r, s, cp: in std_logic;

Q, qb: out std_logic);

End r_s;

Architecture behav of r_s is

Signal rs: std_logic_vector downto 0 (1);

Signal q_s qb_s: std_logic;

The begin

Rs<=s& R;

The process (rs, cp)

The begin

If the cp 'event and cp=' 1 'then

If the rs="11" then q_s & lt;=q_s; Qb_s & lt;=qb_s;

Elsif rs="01" then q_s & lt;=not q_s; Qb_s & lt;='1'.

Elsif rs="10" then q_s & lt;=not q_s; Qb_s & lt;='0'.

Elsif rs="00" then q_s & lt;=not q_s; Qb_s & lt;='X';

End the if;

End the if;

End the process.

Q<=q_s; Qb<=qb_s;

End behav.

Thank you, HHH ~

CodePudding user response:

X is the uncertainty... You this is a software problemCodePudding user response: