Based on the market demand, the ARM company launched its new for the ARMv7 architecture as well as tuning based 32-bit architecture (M3 micro controller core, ST (stmicroelectronics) introduced based on core architecture (M3 - STM32 MCU, STM32 product diversification, high cost performance, simple and easy to use way of library development, in the mid-range MCU market becomes the most shining star,

The timer

As many as seven stm32 timer,

(1) three 16 timer, each timer has as many as four comparison PWM pulse counter or used for input and output channels and incremental encoder input,

(2) a 16-bit with dead zone control and emergency brake, used for motor control PWM advanced control timer,

(3) two independent model and watchdog timer window type,

(4) the system time timer and 24 the decrement counter,

Independent watchdog: based on a dozen decreasing counter and an 8-bit preassigned screen, by a independent 40 KHZ internal rc oscillator with clock, can be run in stop and standby mode, can be as a watchdog to reset the whole system when problems occur, or as a free timer timeout for application management,

Window guard dog: there is a diminishing of seven counter, driven by master clock, with interruption of early warning function, can be frozen in debug mode counter,

Tick timer

Dedicated to real-time operating system, can also be used as a standard of decreasing counter, diminishing 24 counters, automatic reloading function, when the counter is 0 can produce a system maskable interrupt,

Communication interface of stm32

As many as two of the iic interface

Three usart interfaces

2 spi interface 18 m bits/second

Can interface

Usb20. Full interface

Separate interface behind specific experimental

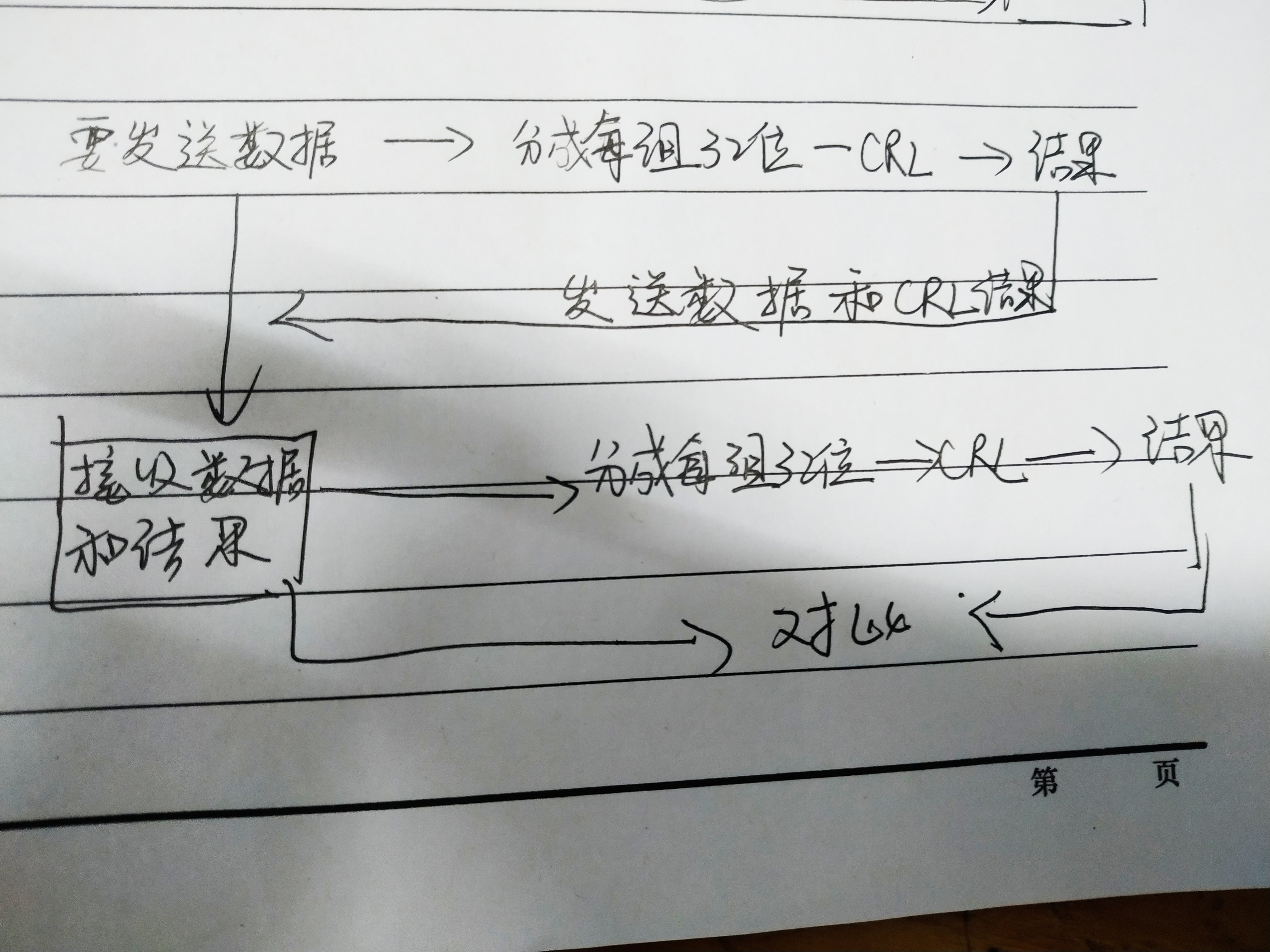

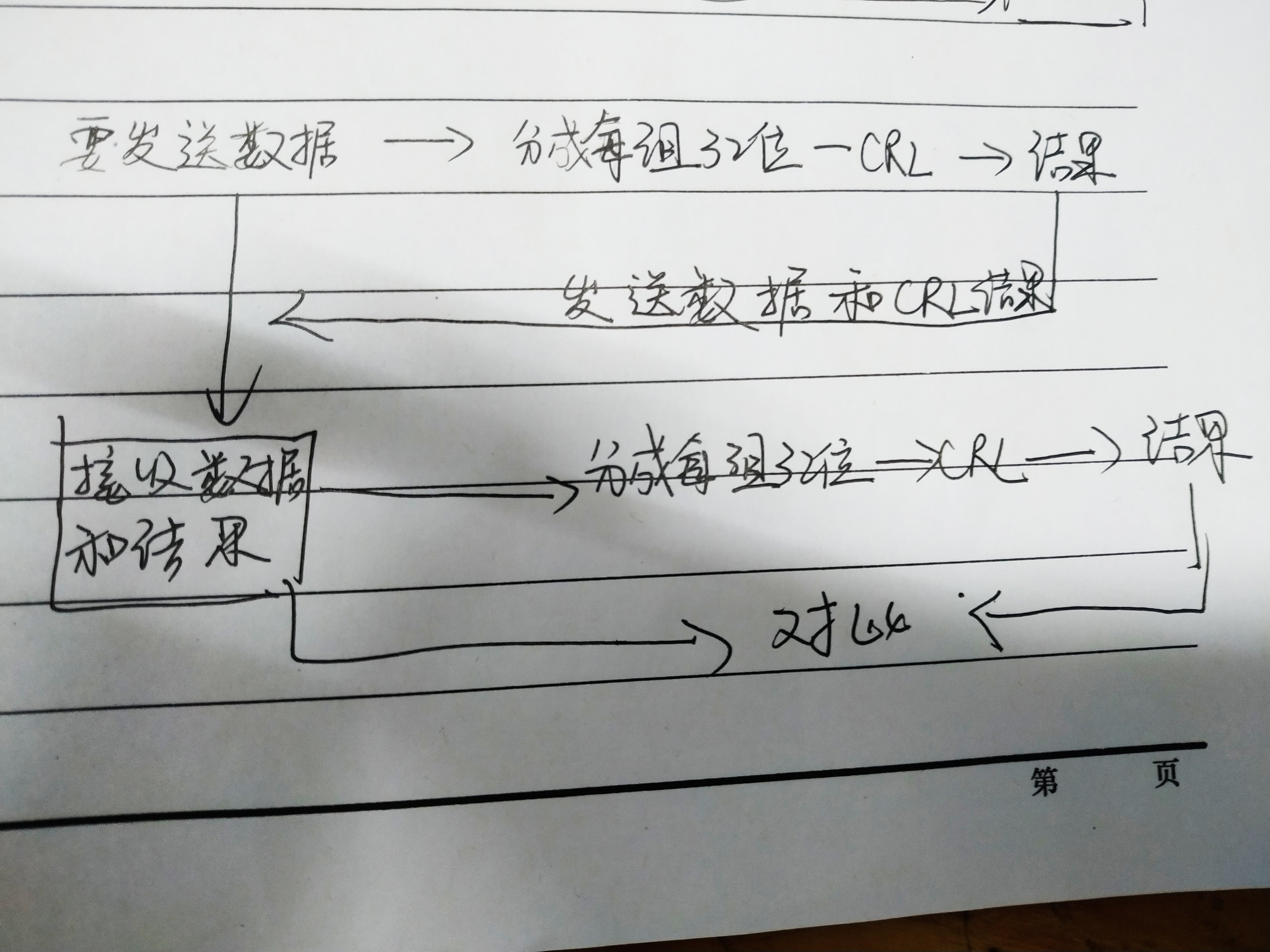

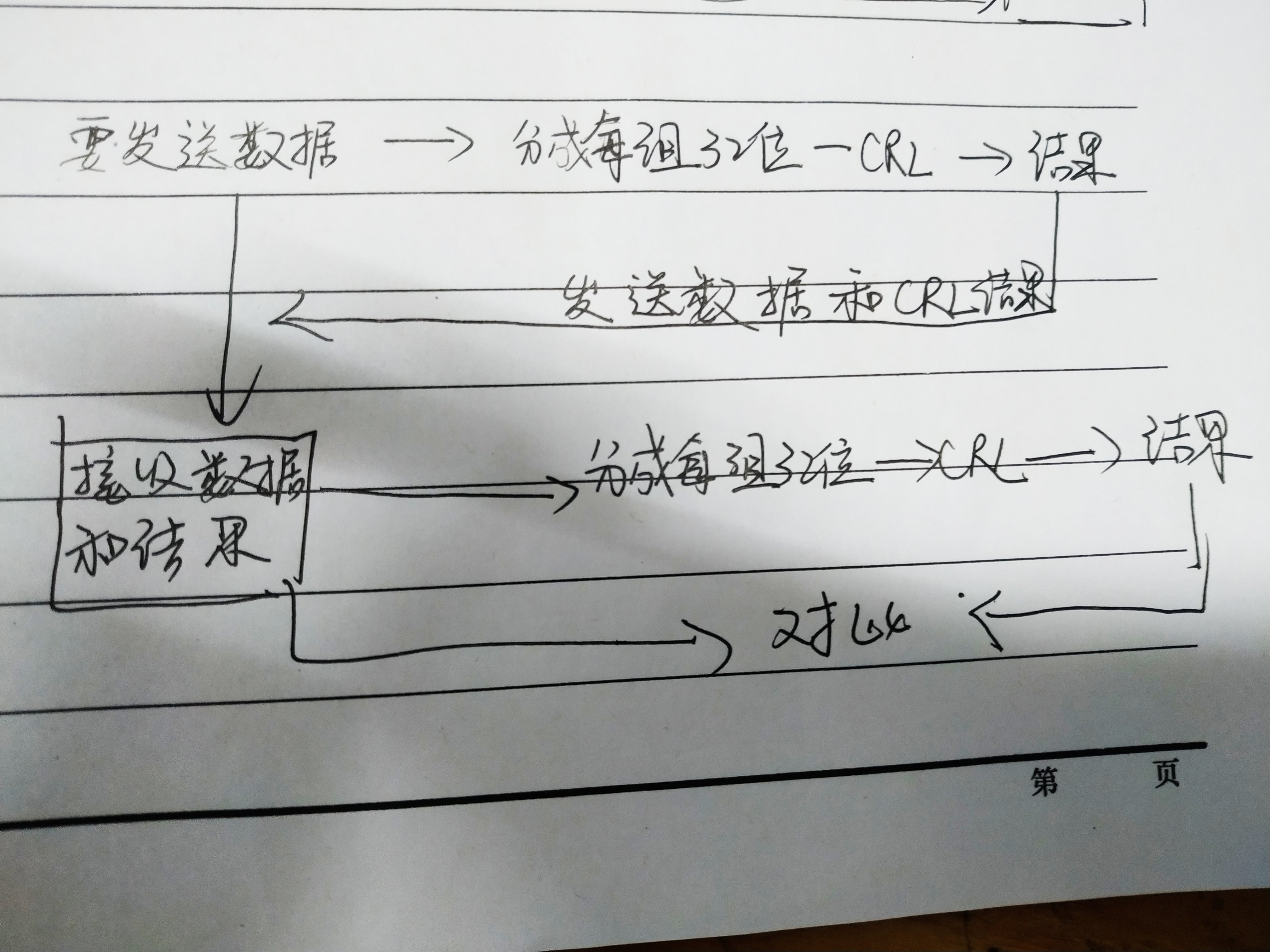

The CRL calculation unit, used for data validity check, is produced by a 32-bit data word, can be applied to the FALSH test

Store

Internal flash memory flash, write good program put the place, the kernel to collect the data through the ICode bus,

Internal SRAM program variables, stack and other overhead are based on the internal SRAM, kernel by DCode bus access,

FSMC English full name is the Flexible static memory controller, the Flexible static memory controller, is a very distinctive stm32f10xx peripherals, can through the FSMC expanded memory, but can only extend static memory, static, sdram can't expand,

AHB to APB bridge

Extend from the ahb bus apb2 and apb1 bus, of peripherals, carrying the stm32 above gpio iic spi serial port are mounted on the two bus,

CodePudding user response:

Post for the first time, the article is a bit simple, illustrated a little wrong,CodePudding user response:

Just not ads, or deleted