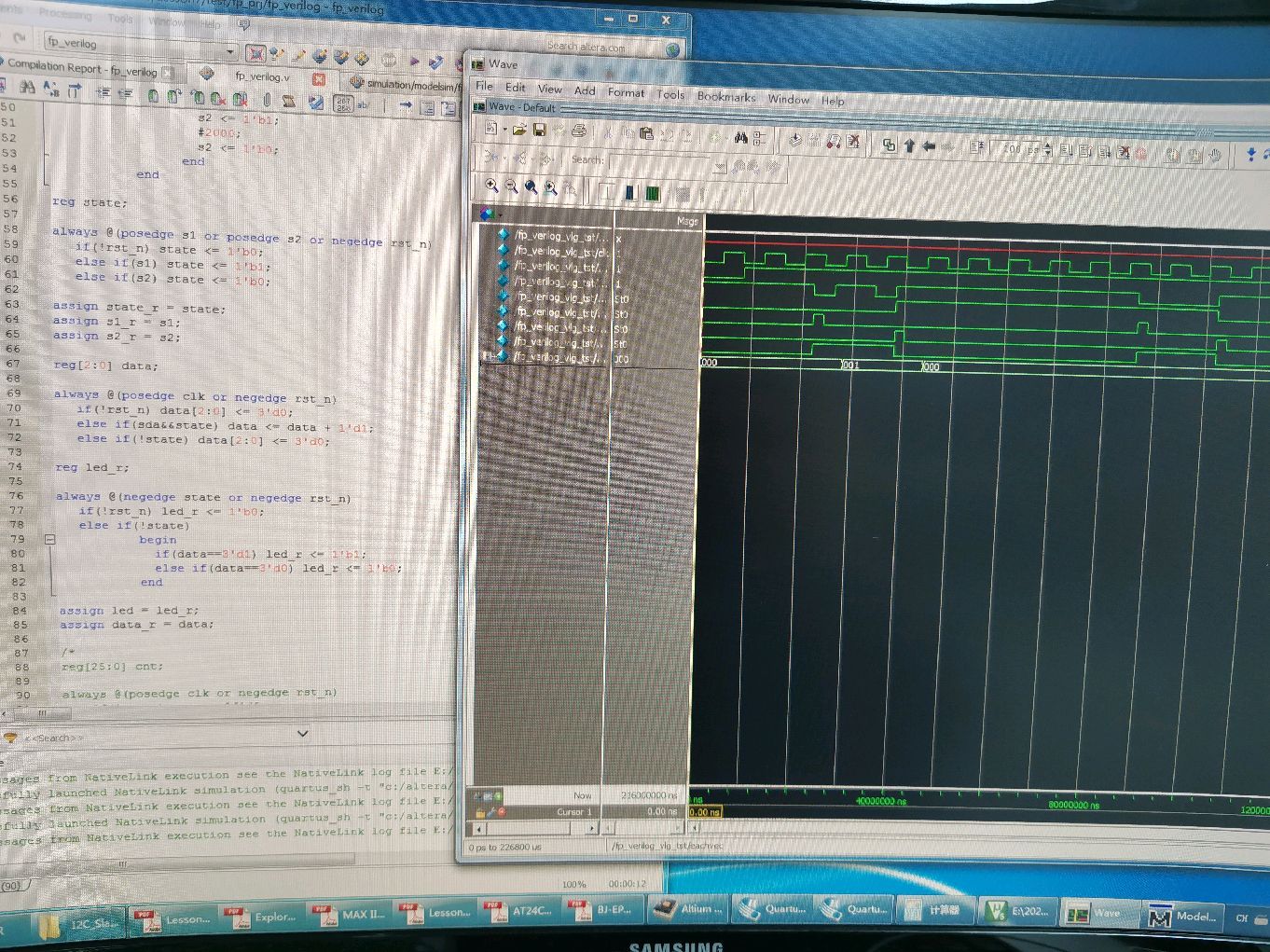

` timescale us/1 us

The module fp_verilog (

CLK, rst_n,

The sda,

Led

);

The input CLK.//the clock signal SCL

Input rst_n;//reset signal low level effective

Input sda.//data signal SDA

The output of led;//indicator light 0-1 - out

Reg s1.

Always @ (negedge sda or negedge rst_n)

if(! Rst_n) s1 & lt;=1 'b0;

else if(! Sda)

The begin

If (CLK)

The begin

S1 & lt;=1 'b1;

# 3000;

S1 & lt;=1 'b0;

End

End

Reg s2.

Always @ (posedge sda or negedge rst_n)

if(! Rst_n) s2 & lt;=1 'b0;

Else if (sda)

The begin

If (CLK)

The begin

S2 & lt;=1 'b1;

# 3000;

S2 & lt;=1 'b0;

End

End

Reg the state;

Always @ (posedge s1 or s2 or negedge of posedge rst_n)

if(! Rst_n) state & lt;=1 'b0;

Else if (s1) state & lt;=1 'b1;

Else if (s2) state & lt;=1 'b0;

Reg [1:0] data;

Always @ (posedge CLK or negedge rst_n)

if(! Rst_n) data [1:0]

else if(! State) data [1:0]

Reg led_r;

Always @ (negedge state or negedge rst_n)

if(! Rst_n) led_r & lt;=1 'b0;

Else if (data=https://bbs.csdn.net/topics/=2 'd1) led_r & lt;=1 'b1;

Else if (data=https://bbs.csdn.net/topics/=2 'd0) led_r & lt;=1 'b0;

The assign led=led_r;

Endmodule

CodePudding user response:

A few warning prompt, the output pin is set as the power supply or the ground, 3 no drive logic input pin, but here I have configured the pinsCodePudding user response:

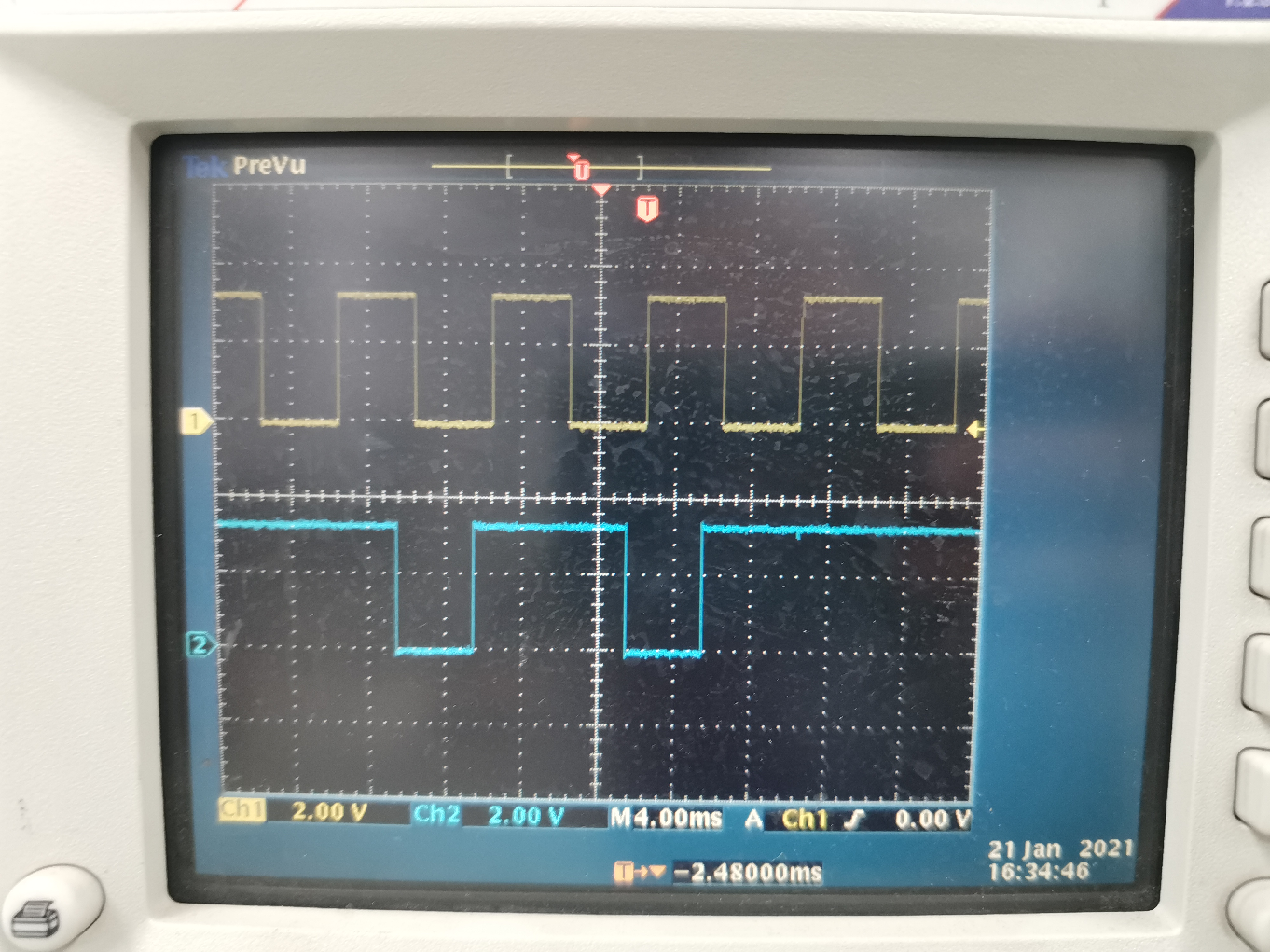

# 3000;Is not comprehensive, can only be used in the simulation,

As a result, s1, s2 after reset is always 0

Didn't look at other code