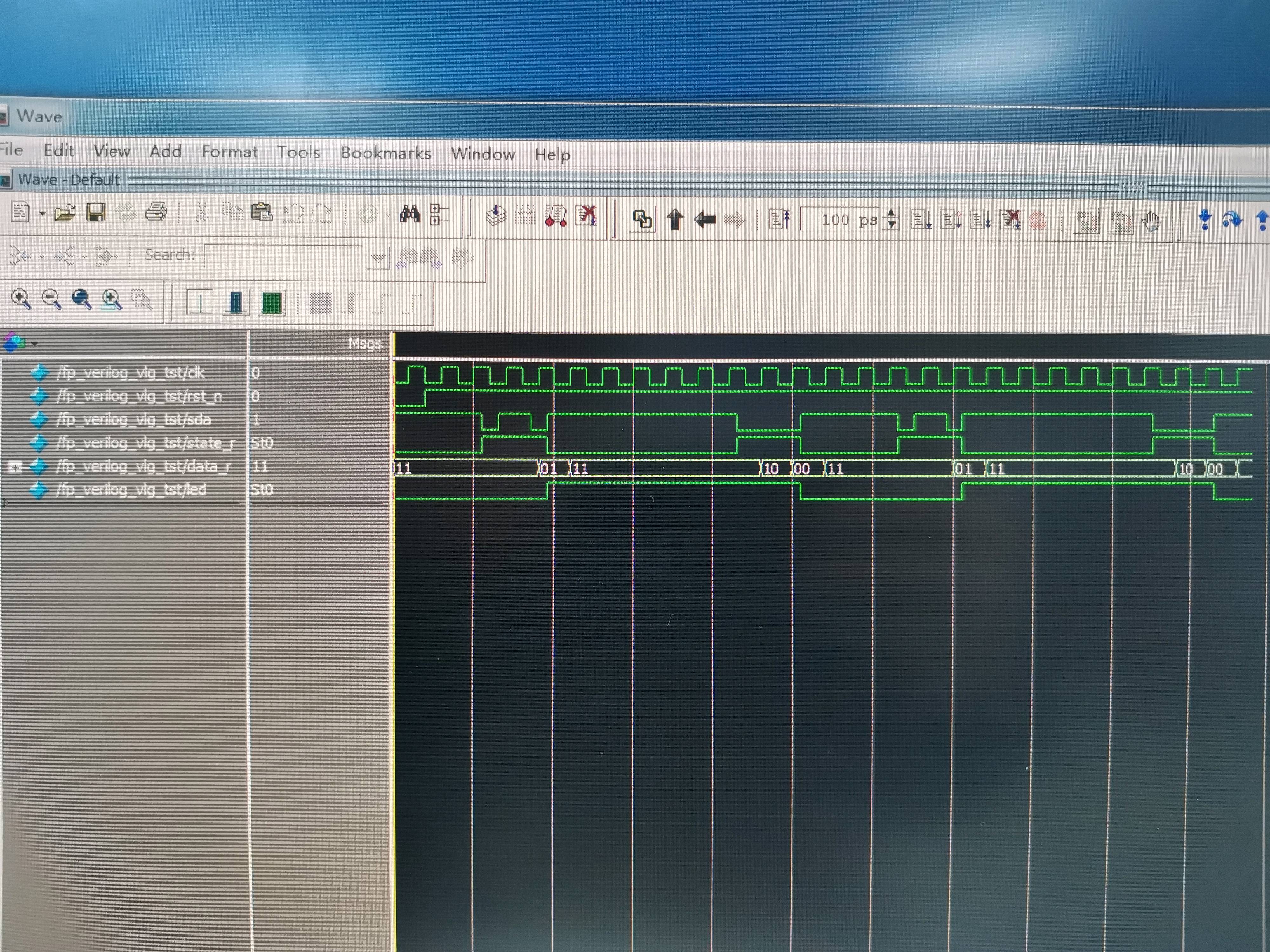

Alarm prompt: 1. The interring latches for variable "s1" and "s2", which doesn its previous value in one or more paths through the always construct

2. The timequest timing analyzer is analyzing two combinational loops as latches.

3. The Timing requirements not met.

The module fp_verilog (

CLK, rst_n,

The sda,

Leds, data_r state_r

);

The input CLK.//the clock signal SCL

Input rst_n;//reset signal low level effective

Input sda.//data signal SDA

The output of led;//indicator light 0-1 - out

The output data_r;

The output state_r;

Wire [1:0] data_r;

Reg s1.

Always @ (negedge sda or negedge CLK or negedge rst_n)

if(! Rst_n) s1 & lt;=1'b0;

Else if (! Sda)

The begin

If (CLK==1 'b1) s1 & lt;=1 'b1;

Else if (CLK==1 'b0) s1 & lt;=1 'b0;

End

Reg s2.

Always @ (posedge sda or negedge CLK or negedge rst_n)

if(! Rst_n) s2 & lt;=1'b0;

Else if (sda)

The begin

If (CLK==1 'b1) s2 & lt;=1 'b1;

Else if (CLK==1 'b0) s2 & lt;=1 'b0;

End

Reg the state;

Always @ (posedge s1 or s2 or negedge of posedge rst_n)

if(! Rst_n) state & lt;=1'b0;

Else if (s1) state & lt;=1 'b1;

Else if (s2) state & lt;=1'b0;

Reg [1:0] data;

Reg [1:0] k;//0-3

Always @ (posedge CLK or negedge rst_n)

if(! Rst_n)

The begin

Data [1:0]

Else if (state)

The begin

Data [k] <=sda;

If (k==2 'k< d1); D0=2 ';

The else k

The else begin

Data [1:0]

Reg led_r;

Always @ (negedge state or negedge rst_n)

if(! Rst_n) led_r & lt;=1'b0;

Else if (data=https://bbs.csdn.net/topics/=2 'b01) led_r & lt;=1 'b1;

Else if (data=https://bbs.csdn.net/topics/=2 'b00) led_r & lt;=1'b0;

/*

Always @ (data)

If (data=https://bbs.csdn.net/topics/=2 'b11) led_r & lt;=1 'b0;

Else if (data=https://bbs.csdn.net/topics/=2 'b01) led_r & lt;=1 'b1;

Else if (data=https://bbs.csdn.net/topics/=2 'b00) led_r & lt;=1'b0;

*/

The assign led=led_r;

The assign data_r=data;

The assign state_r=state;

Endmodule