I'm working on a question on CPU Datapaths for 5-stage RISC and I think I'm misunderstanding how load instructions are handled. Given this datapath:

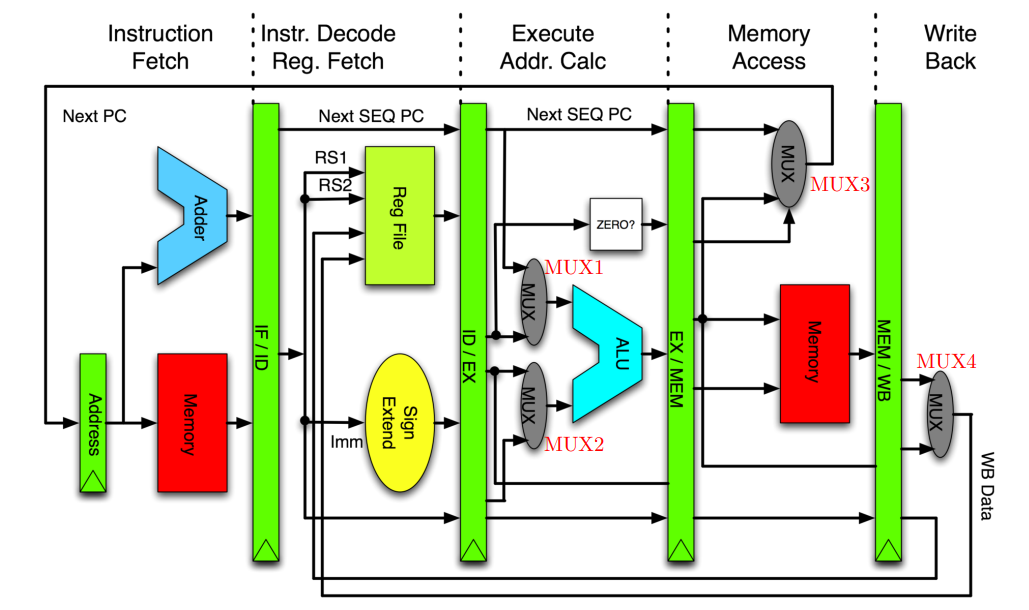

Where MUX1 takes NPC or Src1 Register Data as input, MUX2 takes Src2 Register Data or an immediate value as input, MUX3 takes NPC or the output of the ALU (and sometimes the zero flag for branching) as input, and MUX4 takes ALU output or Memory Data as input.

We are asked to give the inputs to each multiplexer for the instruction "mov R0, [R1 1000]" (Where instructions are of the form "op, dest, src1, src2"). I'm pretty sure that for this instruction R0 would be src1, R1 would be src2 and 1000 would be an immediate value, but I'm lost as to how these should be handled in the execution and memory access stages in order to compute the correct result.

Any help would be appreciated! Sorry if this question was convoluted.

CodePudding user response:

Given the various mismatches in the question, let's look at some scenarios.

First, that mov R0, [R1 1000] loads from effective address R1 1000, and targets R0.

This is both possible and likely, since RISC V, like MIPS (and Intel syntax in x86) specifies the target as the first operand, as you have mentioned with "op dest, src1, src2").

The load instructions are I-Type instructions and have rs1, rd, and imm as instruction fields. Load instructions have one register source, one immediate source and one register target (the one to take on the result read from memory).

MUX1 would choose between NPC (of unknown value in this scenario) and the value coming from register rs1, here R1 (also of unknown value in this scenario). Control signals will cause it to choose rs1, so the value from R1 is MUX1's output.

MUX2 would choose between rs2 and the immediate. There is no rs2 field in an I-Type instruction, but the hardware will still interpret bits 20-24 as a register number and look up that register's value to feed to one of MUX2's inputs. The other input will come from the sign extended immediate, 1000. Obviously, control signals will cause it to choose the immediate over the erroneous rs2 value.

(If we want to, we can determine the register number for rs2 by inspecting the instruction's bits. In this instruction, those bits 20-24 would be from the immediate field, but those bits are still there. At this early point in instruction decode, the hardware doesn't actually know what kind of instruction it is, so it does this rs2 lookup in parallel just in case it is one of the type of instructions that does use the rs2 field. The control signals will tell the succeeding ALU/EX stage to ignore this speculatively performed lookup.)

MUX3 will be given three different inputs, one is NPC, the other is ALU output, which is R1 1000, and the other is another register value. Control signals will tell MUX3 to choose the NPC value (the others are erroneous).

MUX4 will be given the value read from memory at R1 1000 and R1 1000 itself as ALU output. Control signals will tell MUX4 to choose the value read from memory.

Second, it could be that mov R0, [R1 1000] is a store instruction. The value being stored comes from R0 and it is stored at address R1 1000.

Store instructions are S-Type and have rs1, rs2, and imm instruction fields. Store instructions have two register sources and one immediate — there is no register target.

Either way, MUX1, MUX2, and MUX3 operate the same as with the first scenario, since the store instructions, like load instructions, also compute an effective address for memory operation from rs1 imm, here, R1 1000.

MUX4 will be given a choice between some garbage on the memory output (there was no read operation so the output of memory is junk) or the ALU output R1 1000. It doesn't matter what is chosen, since reg write is false and no writeback will happen anyway (it is a store, not a load — the write in a store is into memory not into register).