question:

I just changed files in the device tree, there is no other changes, the initialization in the device tree [gpio - row] and [gpio - col], but because there is no gpio device tree code and order, how to identify the kernel line 4 gpio rows in the order, and 8 column gpio columns in the order? If not sure, so the result should be broken?

the current project specific situation is as follows:

Note: when using the framework, tested each GPIO 4 rows 8 columns, are all controlled, in the device tree is blocking the function of other reuse,

1.1, 14 x14 imx6ul - - evk. DTS file add the following code in the device tree:

Under the root node to add the key node hardware design is 4 rows 8 columns, but in fact only three lines, so the following initialization line 4 directly without initialization)

KPP {

Compatible="gpio - matrix - keypad";//matrix key driver name

Pinctrl - names="default";

Pinctrl - 0=& lt; & Pinctrl_key & gt;;//key IO configuration

Debounce delay - ms=& lt; 20 & gt;;//shaking,

Col - scan - delay - us=& lt; 20 & gt;;//scan delay

/* 4 */

The row - gpios=& lt;

& Gpio2 16 GPIO_ACTIVE_HIGH

& 17 GPIO_ACTIVE_HIGH gpio2

& 18 GPIO_ACTIVE_HIGH gpio2

& 19 GPIO_ACTIVE_HIGH gpio2

& gt;;

/* * 8 column/

Col - gpios=& lt;

& 8 GPIO_ACTIVE_HIGH gpio2

& Gpio2 9 GPIO_ACTIVE_HIGH

& Gpio2 10 GPIO_ACTIVE_HIGH

& 11 GPIO_ACTIVE_HIGH gpio2

& 12 GPIO_ACTIVE_HIGH gpio2

& 13 GPIO_ACTIVE_HIGH gpio2

& 14 GPIO_ACTIVE_HIGH gpio2

& 15 GPIO_ACTIVE_HIGH gpio2

& gt;;

Linux, keymap=& lt;

/* row0 */

MATRIX_KEY (0 x0, 0 x0, KEY_LEFT)

MATRIX_KEY (0 x0, 0 x1, KEY_UP)

MATRIX_KEY (0 x0, 0 x2, KEY_F1)

MATRIX_KEY (0 x0, 0 x3, KEY_X) fx/* */

MATRIX_KEY (0 x0, 0 x4, KEY_7)

MATRIX_KEY (0 x0, 0 x5, KEY_4)

MATRIX_KEY (0 x0, 0 x6, KEY_1)

MATRIX_KEY (0 x0, 0 x7, KEY_M)

Row1/* */

MATRIX_KEY (0 x1, 0 x0, KEY_DOWN)

MATRIX_KEY (0 x1, 0 x1, KEY_RIGHT)

MATRIX_KEY (0 x1, x2, KEY_F2)

MATRIX_KEY (0 x1, 0 x3, KEY_O)/* fo */

MATRIX_KEY (0 x1, 0 x4, KEY_8)

MATRIX_KEY (0 x1, 0 x5, KEY_5)

MATRIX_KEY (0 x1, 0 x6, KEY_2)

MATRIX_KEY (0 x1, 0 x7, KEY_0)

Row2/* */

/* MATRIX_KEY (0 x2, 0 x0, KEY_) */

/* MATRIX_KEY (0 x2, 0 x1, KEY_) */

MATRIX_KEY (0 x2, 0 x2, KEY_ENTER)

MATRIX_KEY (0 x2, 0 x3, KEY_I) fi/* */

MATRIX_KEY (0 x2, x4, KEY_9)

MATRIX_KEY (0 x2, 0 x5, KEY_6)

MATRIX_KEY (0 x2, 0 x6, KEY_3)

MATRIX_KEY (0 x2, 0 x7, KEY_DOT)

Row3/* */

/* MATRIX_KEY (0 x3, 0 x0, KEY_) */

/* MATRIX_KEY (0 x3, 0 x1, KEY_) */

/* MATRIX_KEY (0 x3, 0 x2, KEY_) */

/* MATRIX_KEY (0 x3, 0 x3, KEY_) */

/* MATRIX_KEY (0 x3, 0 x4, KEY_) */

/* MATRIX_KEY (0 x3, x5, KEY_) */

/* MATRIX_KEY (0 x3, 0 x6, KEY_) */

/* MATRIX_KEY (0 x3, 0 x7, KEY_) */

& gt;;

Gpio - activehigh;//that must be combined with, or test button will always hang

The status="okay";

}; Adding GPIO iomuxc reuse node reuse:

pinctrl_key: kpp_grp {

FSL, pins=& lt;

/* line row: output mode, take turns to output high level, at the same time can only have a high level */

MX6UL_PAD_SD1_CMD__GPIO2_IO16 0 x10b0

MX6UL_PAD_SD1_CLK__GPIO2_IO17 0 x10b0

MX6UL_PAD_SD1_DATA0__GPIO2_IO18 0 x10b0

MX6UL_PAD_SD1_DATA1__GPIO2_IO19 0 x10b0

/* the column column: input mode, collection level, when the switch is 0, switch to press 1 */

MX6UL_PAD_ENET2_RX_DATA0__GPIO2_IO08 0 xf080

MX6UL_PAD_ENET2_RX_DATA1__GPIO2_IO09 0 xf080

MX6UL_PAD_ENET2_RX_EN__GPIO2_IO10 0 xf080

MX6UL_PAD_ENET2_TX_DATA0__GPIO2_IO11 0 xf080

MX6UL_PAD_ENET2_TX_DATA1__GPIO2_IO12 0 xf080

MX6UL_PAD_ENET2_TX_EN__GPIO2_IO13 0 xf080

MX6UL_PAD_ENET2_TX_CLK__GPIO2_IO14 0 xf080

MX6UL_PAD_ENET2_RX_ER__GPIO2_IO15 0 xf080

& gt;;

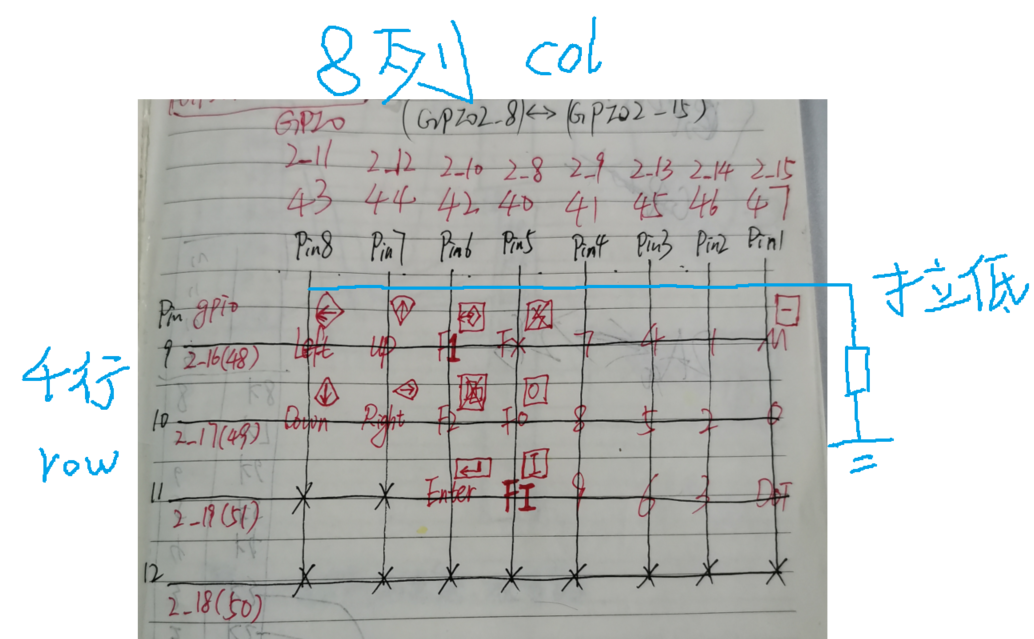

}; 1.2 the keyboard design schematic diagram below

For the logic of the keyboard I understand is:

- (1) 8 column GPIO initialized to input, used to test the pin level, because the default lower, so the detection of high level,

Line 4 - (2) GPIO initialized to output low level, polling output 1, at the same time can only have a high level,

1.3 the current phenomenon of

After the system startup using the command:

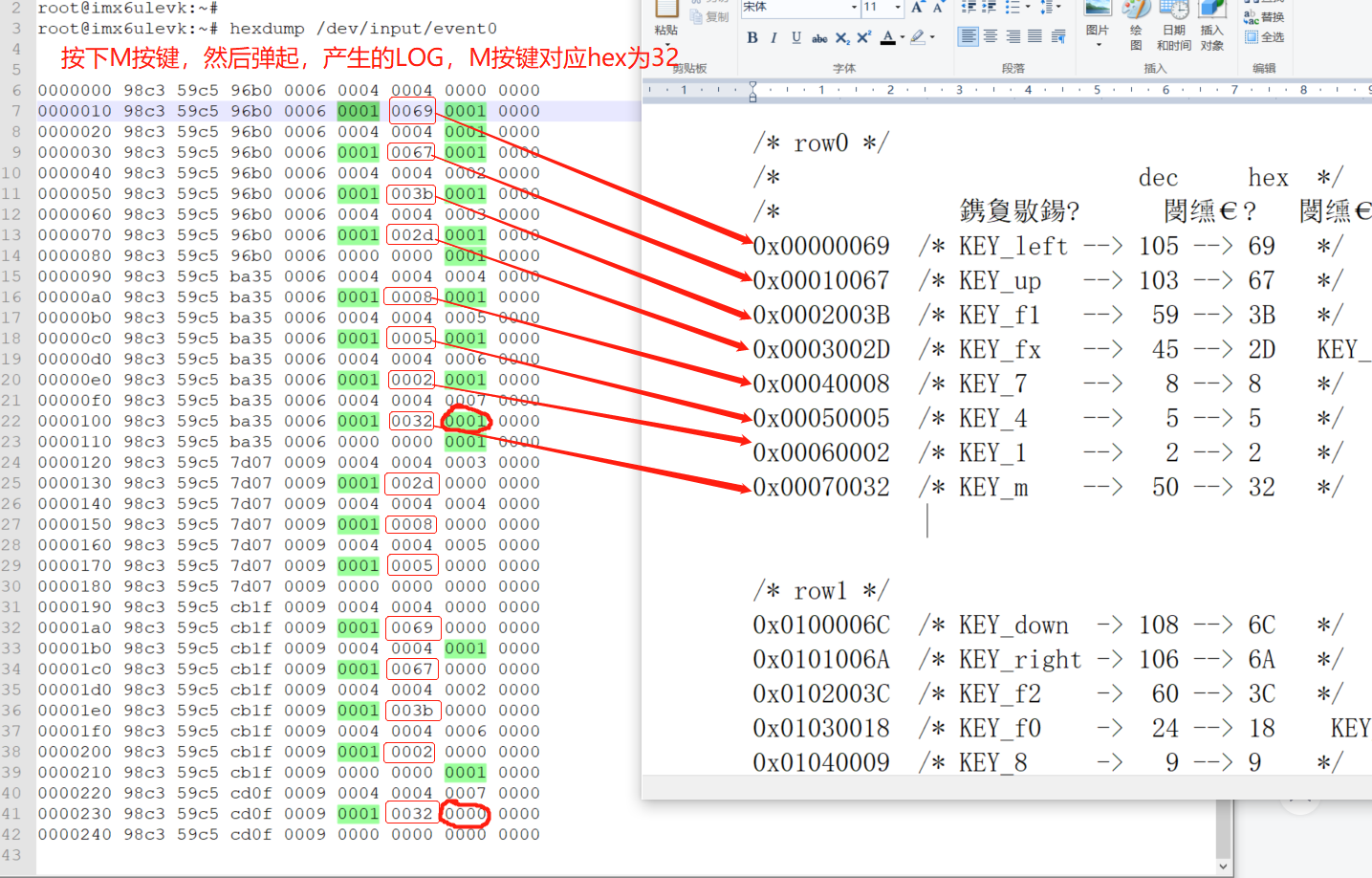

The hexdump)/dev/input/event0

1, then the terminal began to crazy to print, but the first row of keys (left, up, F1, Fx, 7,4,1, M] after press, interrupt stop printing, loosen the continue crazy printing,

2, the other key useless,

bosses genuflect is begged help analysis reason, appreciate!!!!!!

CodePudding user response:

The latest progress, in the original configuration in the device tree is flawed, amend the device tree to do the following:1, first temporarily disable row2/3/4, only keep row1 to debug, namely the GPIO2_16,

2, GPIO2_16 configured to: [& amp; gpio2 16 GPIO_ACTIVE_LOW]

3, 8 a col or configured to: [& amp; 8 GPIO_ACTIVE_HIGH gpio2]

Then I button press next and pop-up M, which is the first line of the edge of the keys, to produce the following log, could you tell me whether normal: