Recently in writing STM32F103 to read and write

AT24C01 chip, using iic hardware block and software simulation two ways to read and write the eeprom is not successful, AT24C01 and AT24C01A/02/04/08 A/16 A temporal series, speaking, reading and writing and requirements, and no AT24C01 data manual Device Address (Device Address), the principle diagram is also no Address comparator, speaking, reading and writing control are useless to Device Address, internal byte block only eeprom Address (Word Address), as shown in the figure below, my brother elder brother of the fire and atomic read and write AT24C02 procedures related to first send A Device Address (0 xa0) that part of the program to delete, speaking, reading and writing is not successful, the program stuck not successful), not deleted successful (read and write data, read data is always 0 XFF or 0 x00), moreover AT24C01 below 5 v only support 100 KHZ, and I also try to modify the delay function, but still can't read and write success (read data often is 0 XFF, i.e., 255), want to ask next everybody on the issue of the read/write AT24C01, be obliged!

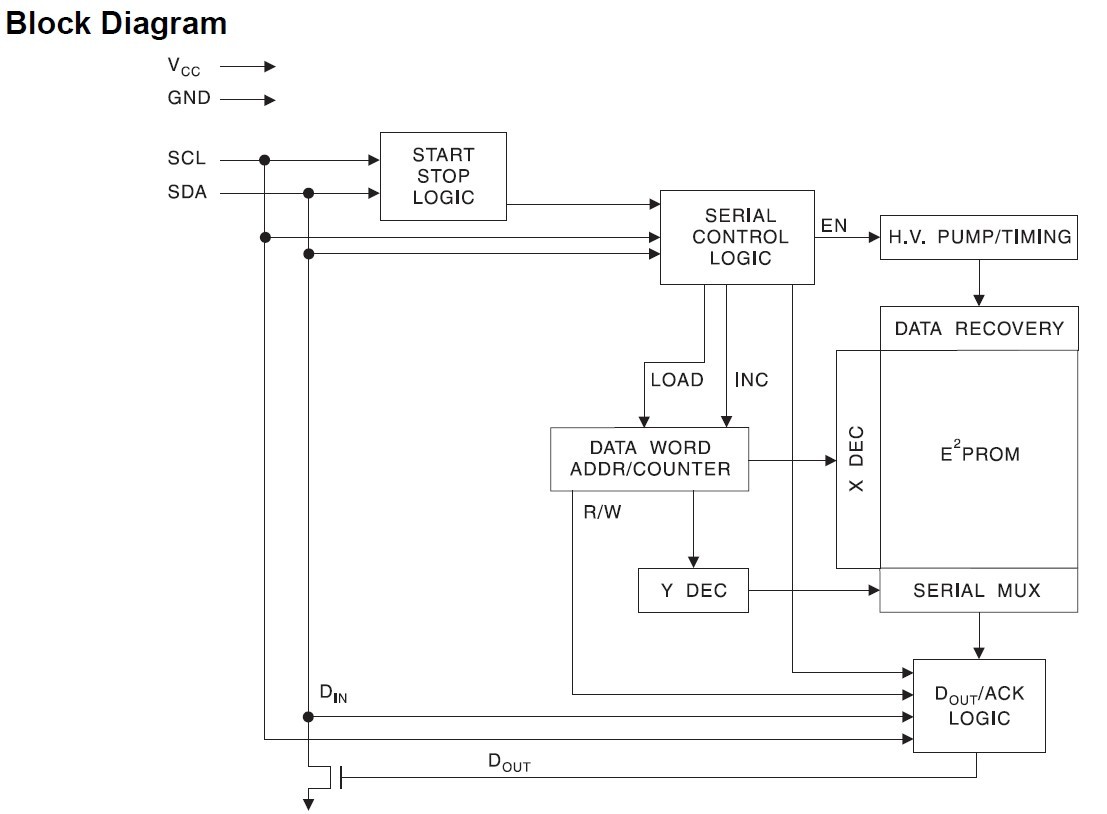

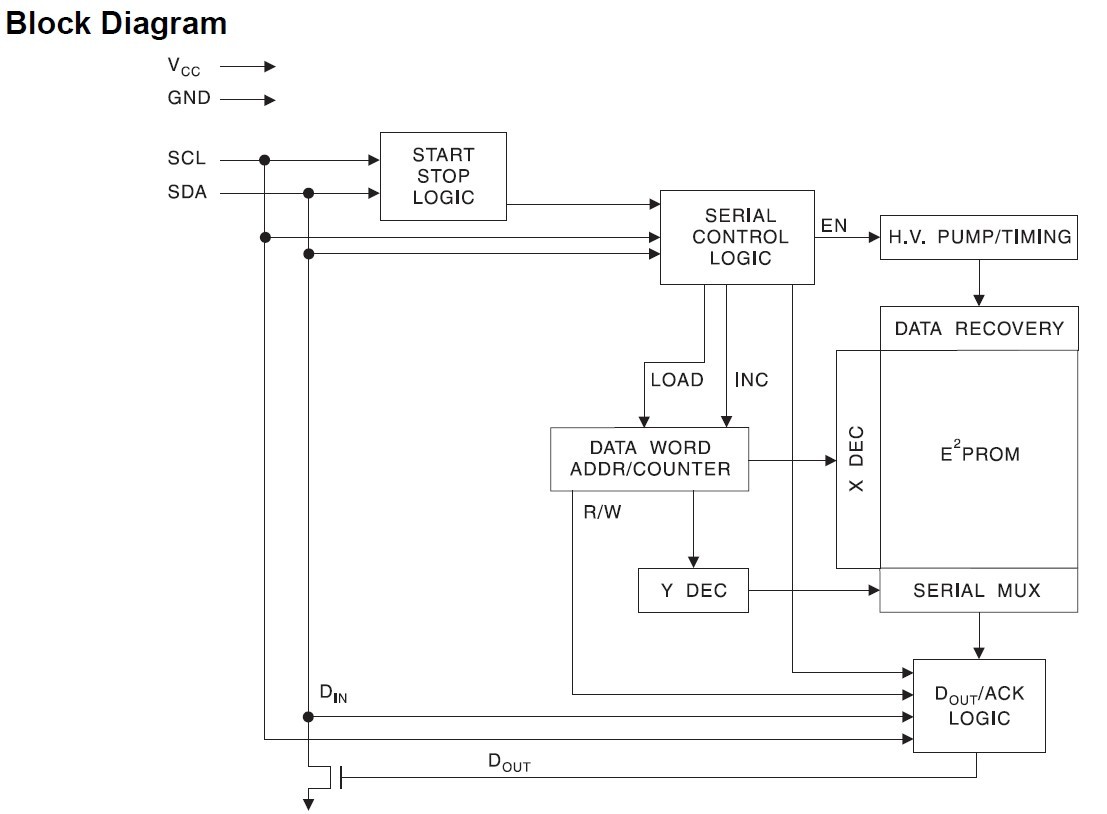

The principle diagram of the

AT24C01

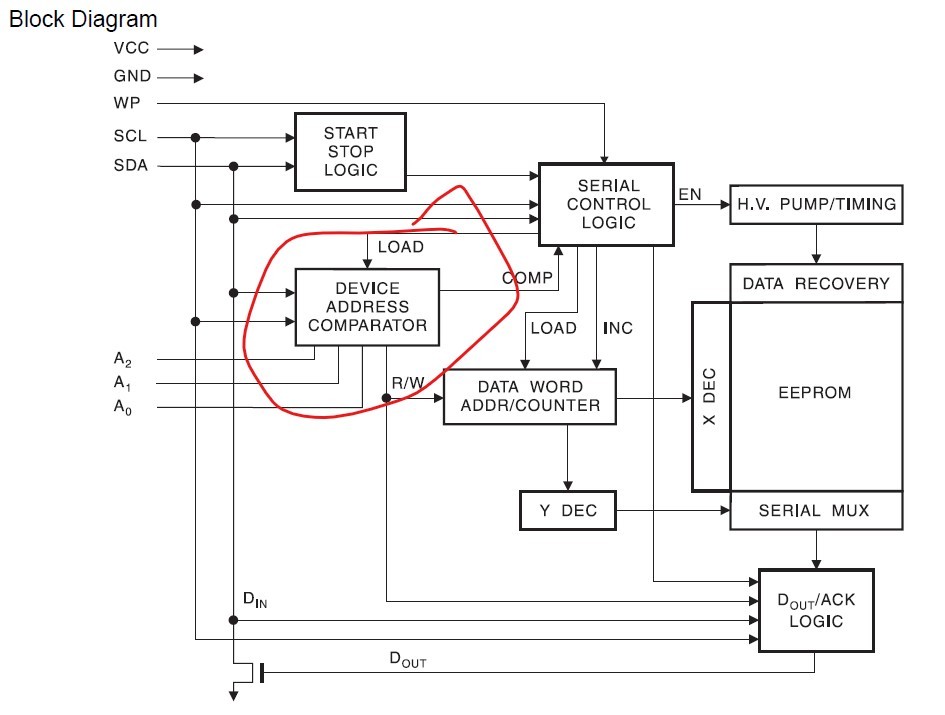

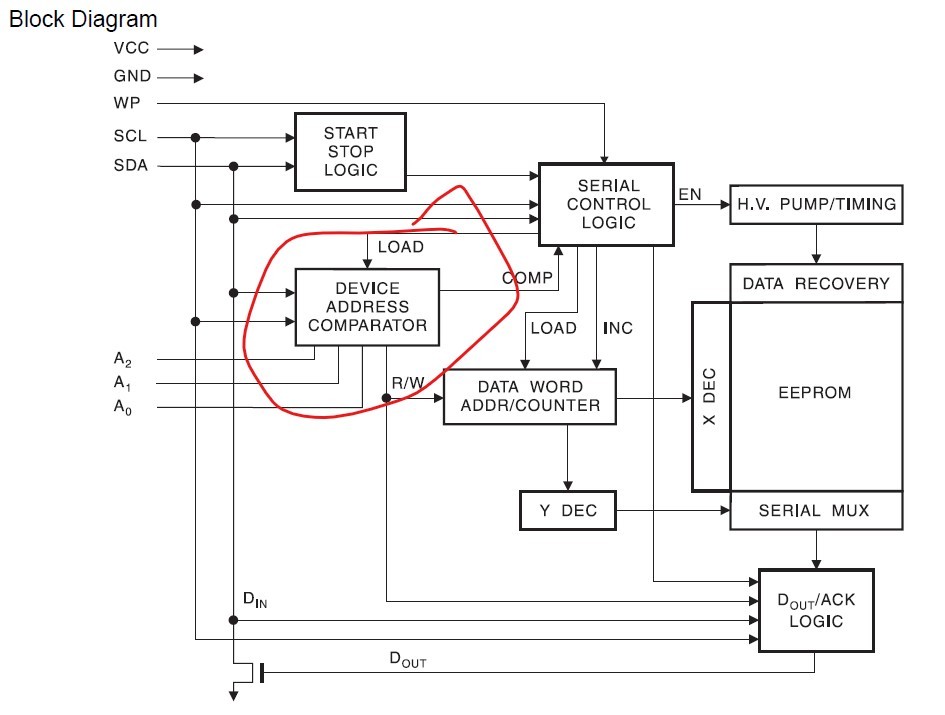

The principle diagram of the

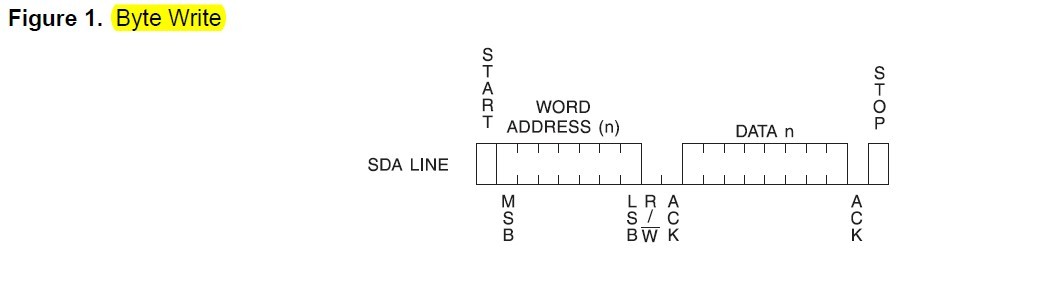

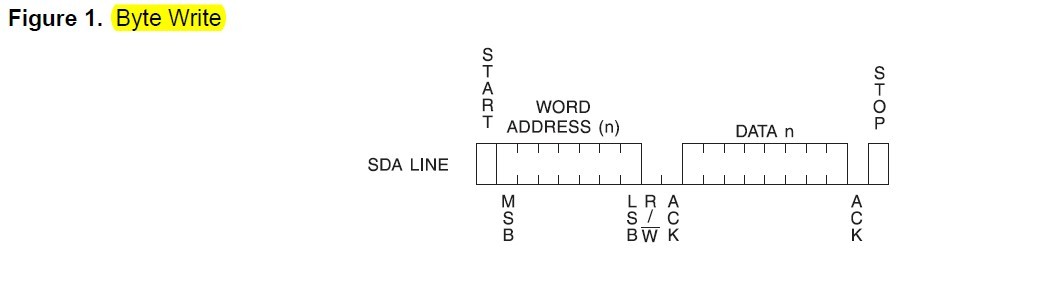

AT24C02  AT24C01 write sequence

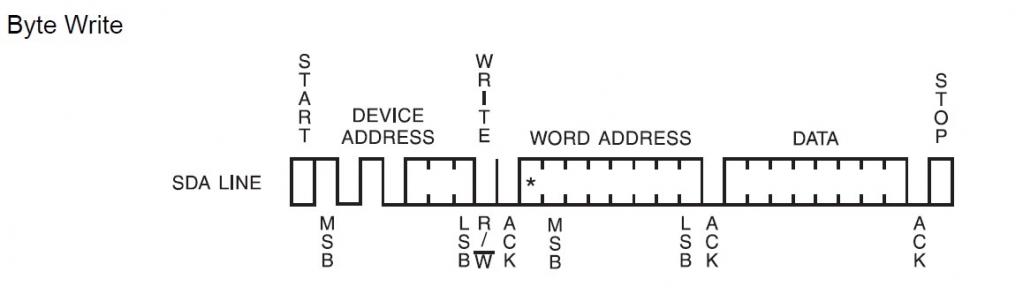

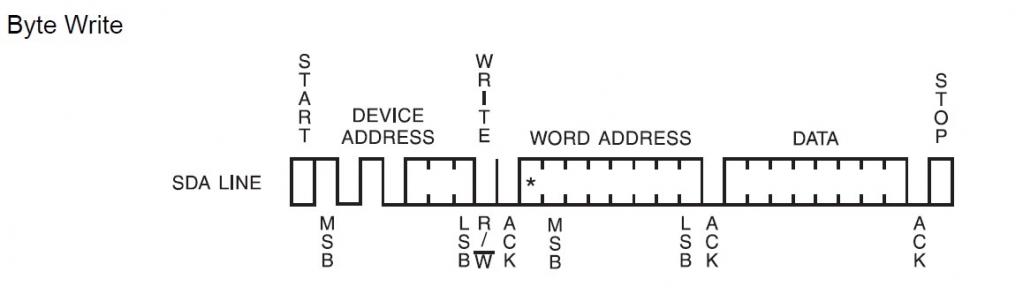

AT24C01 write sequence  write AT24C02 sequence

write AT24C02 sequence

CodePudding user response:

AT24C01 data sheet in this post in the following I can find a

https://www.firebbs.cn/forum.php? Mod=viewthread& Tid=31328 & amp; Extra=