[align=center]

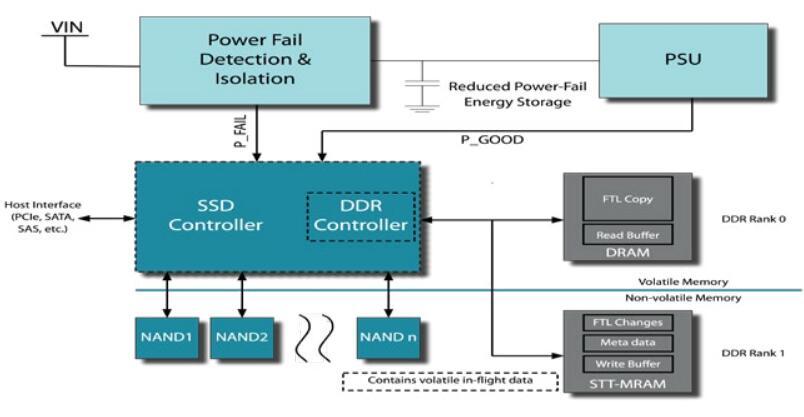

Figure 1 has power failure protection function of hybrid DDR/STT - MRAM SSD architecture [/align]

For enterprise-class solid-state drives, the design of the power management system is very important, the system must detect a power failure, will drive from the host, and enough energy stored to support drives to allow any running data submitted to the nonvolatile memory, in order to ensure data integrity, keep the energy required to complete this operation and the amount of data in the flight, the speed of the nonvolatile memory and is directly proportional to the power consumption of the system, can provide the amount of time will this keep energy storage as power failure window or in running out of energy before can be used to store not protected data time,

To support heterogeneous composed of different levels of different types of memory DDR architecture, ideally, SSD controller contains DDR controller needs to support processing STT - different timing of MRAM and addressing requirements, in order to achieve the best performance, SSD controller must also adopt other logic to properly manage the DDR controller resident is transfer a small amount of data in the buffer, to ensure that the power line refresh to STT - before MRAM and close all open the pages of the STT - MRAM,