Choose in Xilinx FPGA development of block ram (see pg058) as ram read and write operations,

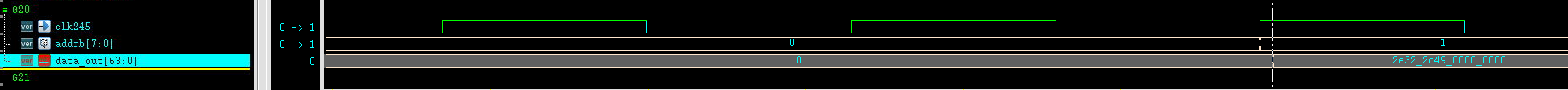

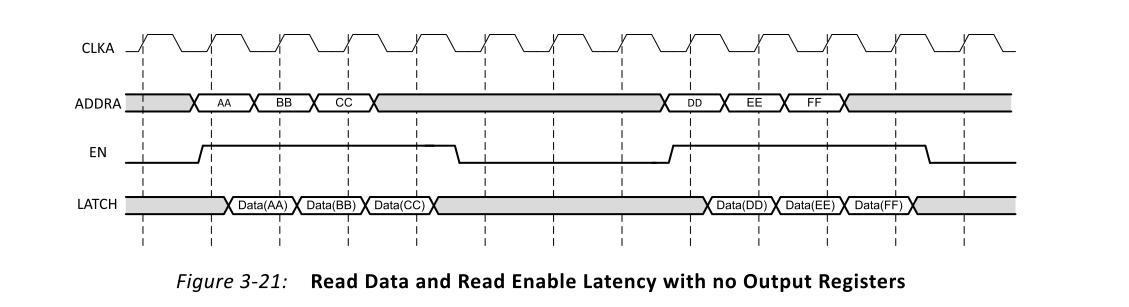

100 ps delay exist in the process of reading data, as shown in figure

Regarding the delay, in pg058 57, relevant time-series show, but there is no delay making detailed explanation of the 100 ps

Everyone a great god, and have to have understanding of the 100 ps delay? Please comment, thank you!!!!!

CodePudding user response:

Expected time is how much or how much time is reasonable, look at the percentage deviation

CodePudding user response:

reference 1st floor dceacho response: expected time is how much or how much time is reasonable, look at the percentage deviation CodePudding user response:

refer to the second floor, please call me Mr Chicken dishes response: Quote: refer to 1st floor dceacho response: CodePudding user response:

reference dceacho reply: 3/f Quote: refer to the second floor, please call me Mr Chicken dishes response: Quote: refer to 1st floor dceacho response: CodePudding user response:

Hello, this problem can you solve it, I met this problem, in the process of simulation is to find a lot of materials also didn't find useful explanation, could you please explain this to me CodePudding user response:

f _ on the safety reference flowers ___, please reply: hello, this problem can you solve it, I met this problem, in the process of simulation is to find a lot of materials also didn't find useful explanation, could you please explain this to me? CodePudding user response:

Have a look at The memory/RAM DDR/LPDDR standard spec, there's a bit thin, such as "The read latency (RL) is defined from The last rising edge of The clock that of a read command (Ex: The second rising edge of The CAS - 2 command) to The rising edge of The clock from which The tDQSCK delay is measured. T",