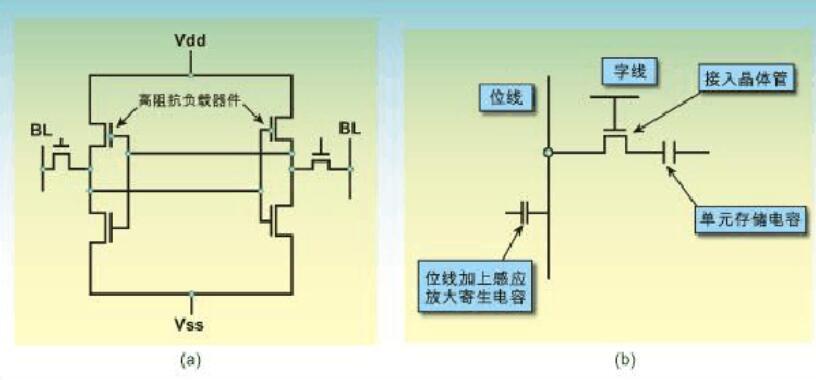

As shown in figure 1 a, as shown in the basic mixed coupling latch and active load cell formed 6 t storage unit, the unit can be used for capacity from several to several one million - bit memory array,

Carefully designed this memory array can satisfy the performance requirements of many different, specific requirements depending on whether or not the designer to choose for high performance and low power optimization of CMOS technology, the production of high-performance SRAM block access time at 130 nm process can easily below 5 ns, and the production of low power memory block access time - with more than 10 ns,

Storage unit of the static characteristic that requires only a few of the auxiliary circuit, only need to address decoding and enabling signal can design a decoder, detecting circuit and the sequential circuits,

Along with the development of the generation of more advanced technology nodes, the characteristics of the device size is more and more small, the use of traditional storage unit made six transistor static RAM can provide more and short access time and smaller cell size, but the leakage current and sensitivity to the soft fault is on the rise, the designer must increase in external circuit to reduce leakage current, and provides the fault detection and correction mechanisms to "erase" the soft failure of the memory,

Figure 1 a: six typical static RAM memory cell transistor, figure 1 b: typical single transistor/single capacitance dynamic memory storage unit,

The limitations of the current 6 tsocram unit

However, used to form a latch and high-performance load six transistor to 6 t cell size is large, thus greatly limits the storage capacity can be realized in the memory array,

This limitation is a major cause of the consumption of the memory block area and because of the node used to implement the chip design technology technology (130,90,65 nm) unit caused by the leakage, as the area of the memory array of the chip area is increased, the ratio of chip size and cost is becoming more and more big,

Leakage current can also be more than the entire power budget or limitation of 6 t cell in the application of portable devices, more large area or high leakage chips final target price may not be able to meet the application requirements, thus unable to become an economic solution,

Alternative technologies as 6 t RAM unit 1 t cell

To the requirements on the large capacity storage (usually greater than 256 KB), but does not require the absolute fastest access time is another solution of the application of technology, the array functions as an SRAM memory used in the solution, but is based on a similar dynamic RAM used single transistor/single capacitance (1 t) storage unit (FIG. 1 b),

CodePudding user response:

Along with the development of the generation of more advanced technology nodes, the characteristics of the device size is more and more small, the use of traditional storage unit made six transistor static RAM can provide more and short access time and smaller cell size, but the leakage current and sensitivity to the soft fault is on the rise, the designer must increase in external circuit to reduce leakage current, and provides the fault detection and correction mechanisms to "erase" the soft failure of the memory,CodePudding user response:

Storage unit of the static characteristic that requires only a few of the auxiliary circuit, only need to address decoding and enabling signal can design a decoder, detecting circuit and the sequential circuits,