Writing your own test bench file:

` timescale ns/1 ps

The module my_first_fpga_vlg_tst ();

Reg CLOCK_50;

Reg [0-0] KEY;

Wire [3-0] LEDR;

My_first_fpga i1 (

//the port map - the connection between the master ports and signals/registers

. CLOCK_50 (CLOCK_50),

The KEY (KEY),

. LEDR (LEDR)

);

Initial the begin

CLOCK_50=0; KEY=0;

# 100;

KEY=1;

# 500 $stop;

End

Always begin

# 5 CLOCK_50=~ CLOCK_50;

End

Endmodule

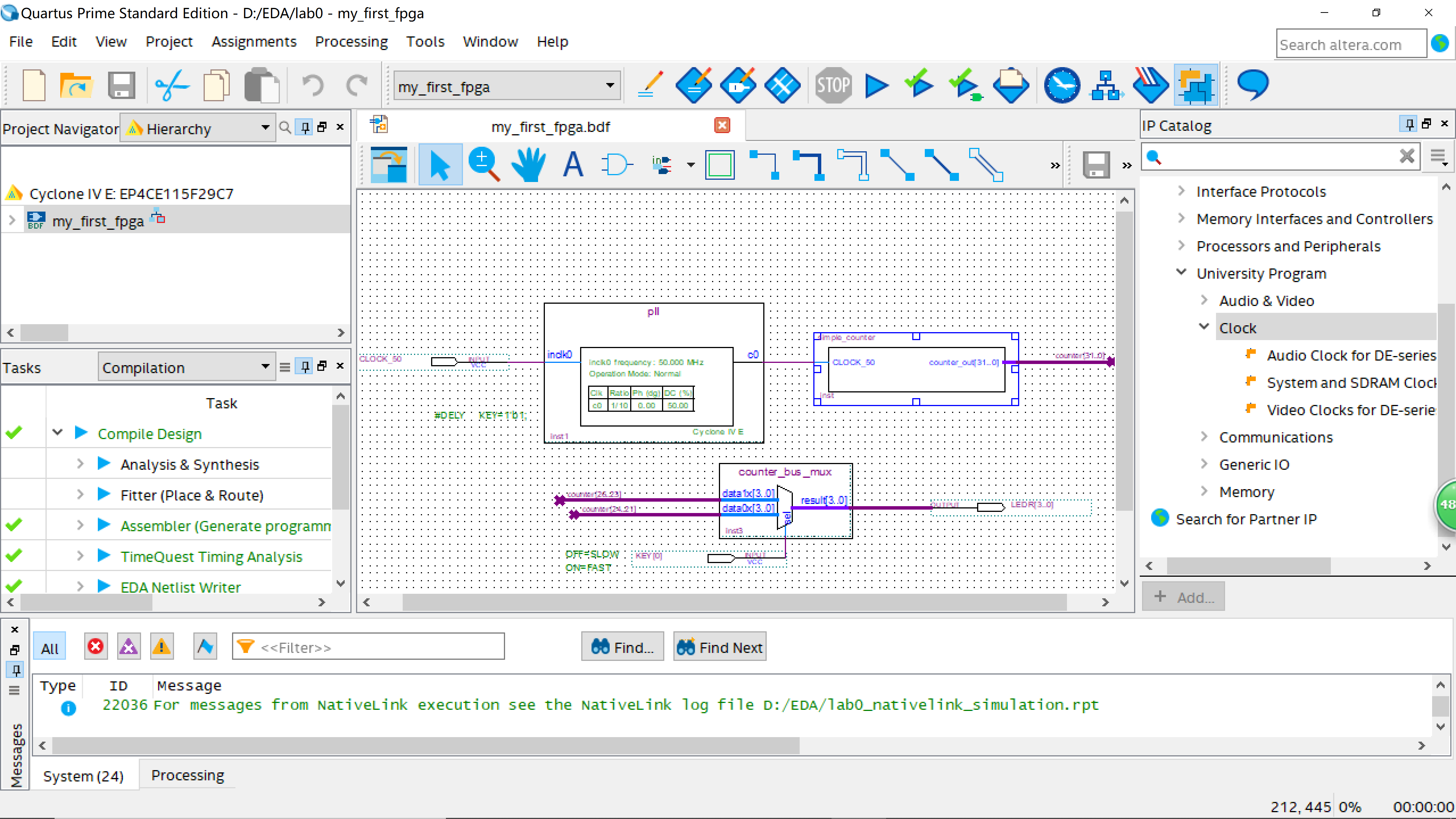

The ModelSim simulation results LEDR has been 0000